单周期处理器设计——基于Logisim的MIPS-Lite2实现

需积分: 0 34 浏览量

更新于2024-08-05

1

收藏 700KB PDF 举报

"Project1_Logisim完成单周期处理器开发1"

本文将详细介绍如何使用Logisim工具设计一个单周期处理器。单周期处理器是一种微处理器架构,它在单个时钟周期内完成指令的取指、译码、执行以及数据的读写等一系列操作。这个项目的目标是基于MIPS-Lite2指令集实现一个单周期处理器,支持如addu、subu、ori、lw、sw等基本指令,并具备溢出检查功能。

一、设计概述

1. 功能需求

处理器需要支持MIPS-Lite2指令集中指定的运算指令,例如addu和subu,同时应具备溢出检测功能,用于处理整数加减运算时可能出现的溢出情况。

2. 设计原则

处理器设计为单周期,这意味着所有操作都在一个时钟周期内完成,简化了设计但可能牺牲了速度。设计时需遵循模块化和层次化的原则,便于理解和维护。

3. 设计视图

设计视图应包括以下几个关键部分:指令单元(IFU)、逻辑运算单元(ALU)、通用寄存器文件(GPR)、数据存储器(DM)、扩展单元(EXT)、多路选择器以及控制单元(Cntroller)。

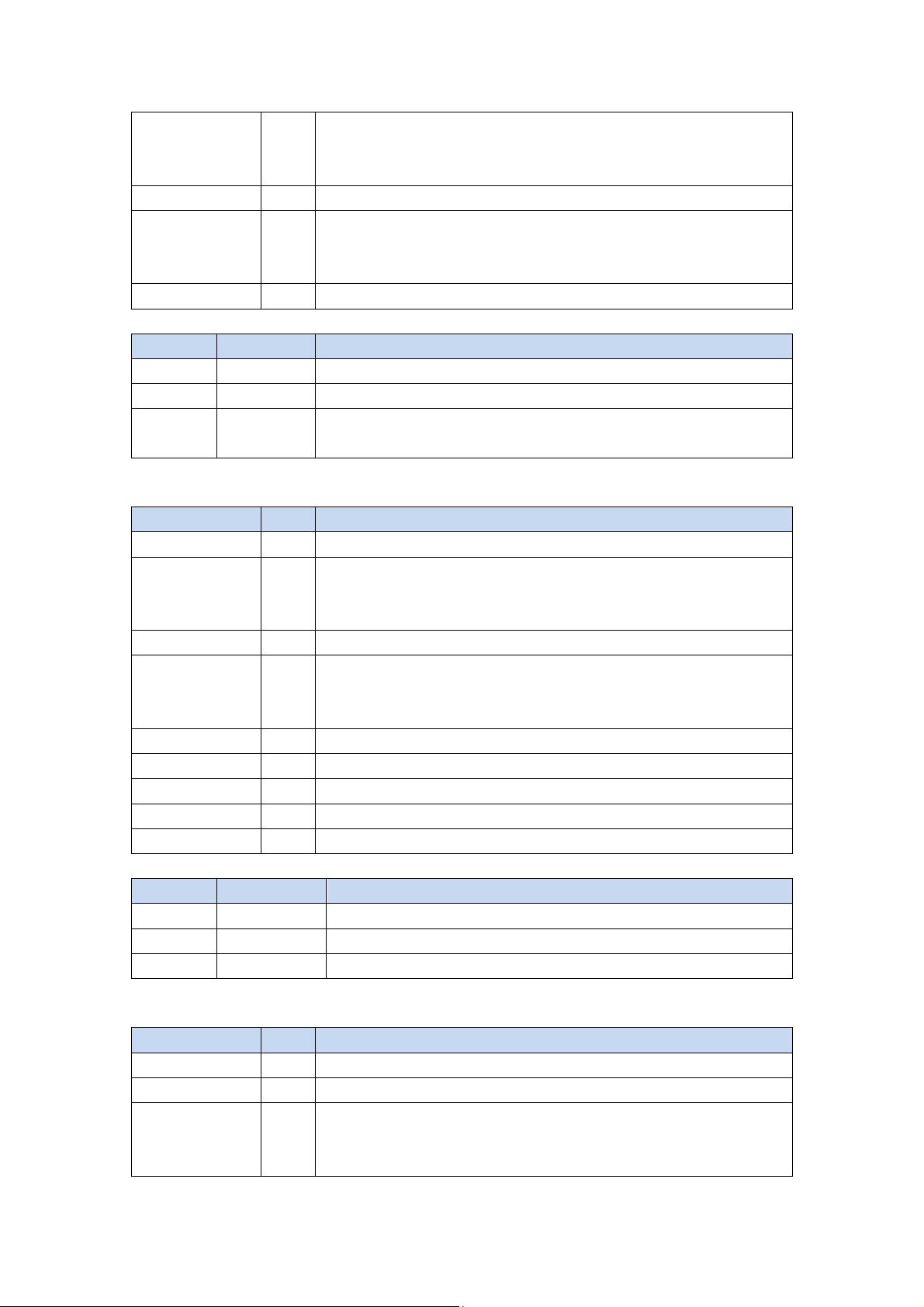

二、模块接口

1. IFU模块

IFU主要包括程序计数器(PC)和指令存储器(IM)。PC用于提供下一条指令的地址,IM则存储指令,此处容量为32bit×32字。由于IM的地址线只有5位,所以最多可存储32个32位指令。

2. GPR模块

GPR包含32个32位的通用寄存器,用于暂存数据和运算结果。

3. ALU模块

ALU负责执行加法、减法和其他逻辑运算。在进行加减运算时,必须考虑到溢出的情况。

4. EXT模块

EXT作为扩展单元,可用于处理特定的运算需求,例如位扩展。

5. DM模块

DM是一个数据存储器,具有读写功能,容量为32bit×32字,采用双端口RAM设计,允许同时读写操作。

6. 控制单元

控制单元Cntroller根据指令信息产生相应的控制信号,驱动整个处理器的运行。

三、设计要求

1. 所有模块都必须有明确的输入输出接口,例如 clk(时钟)、reset(复位)等。

2. 设计文件目录应结构清晰,类似给定示例的结构。

3. 使用Logisim的内置组件,如ROM、RAM和门电路,来构建处理器的各个部分。

四、设计实现

参照提供的IFU模块示例,每个模块应定义清晰的输入输出信号,如IFU中的IfBeq、IM的数据输入输出等。注意,所有信号都应是有效的驱动信号,非端口信号不应包含在设计中。设计完成后,应能在Logisim环境中模拟验证处理器的功能正确性。

总结,本项目通过Logisim工具实现了一个支持MIPS-Lite2指令集的单周期处理器,设计中涵盖了指令获取、数据处理、存储访问等多个关键环节,并强调了模块化和层次化的设计方法,确保了设计的可读性和可维护性。在实际操作中,设计师需要详细理解每个模块的工作原理,合理安排信号连接,以确保整个处理器的协调运作。

2019-04-08 上传

2022-08-08 上传

2021-10-03 上传

2022-08-03 上传

2024-08-01 上传

2022-07-10 上传

2024-08-01 上传

2022-08-08 上传

2022-08-03 上传

生活教会我们

- 粉丝: 33

- 资源: 315

最新资源

- diagwiz:ASCII图作为代码

- userscripts:一些改善UI的用户脚本

- bsu:FAMCS BSU(专业计算机安全)上用于大学实验室的资料库

- krip:彻底的简单加密,在后台使用WebCrypto

- 费用追踪器应用

- 111.zip机器学习神经网络数据预处理

- 财务管理系统

- NNet:用于手写识别的神经网络

- 加州阳光咖啡书吧创业计划书.zip

- Pricy - Amazon Price Watch-crx插件

- AMONG_py-0.0.3-py3-none-any.whl.zip

- MIUI12.5-其他:MIUITR Beta其他语言翻译

- SnowCat:薛定谔的猫

- AMD-1.2.1-py3-none-any.whl.zip

- Slider popover(iPhone源代码)

- 实现一个3D转盘菜单效果