DDR4内存子系统硬件与布局设计要点

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

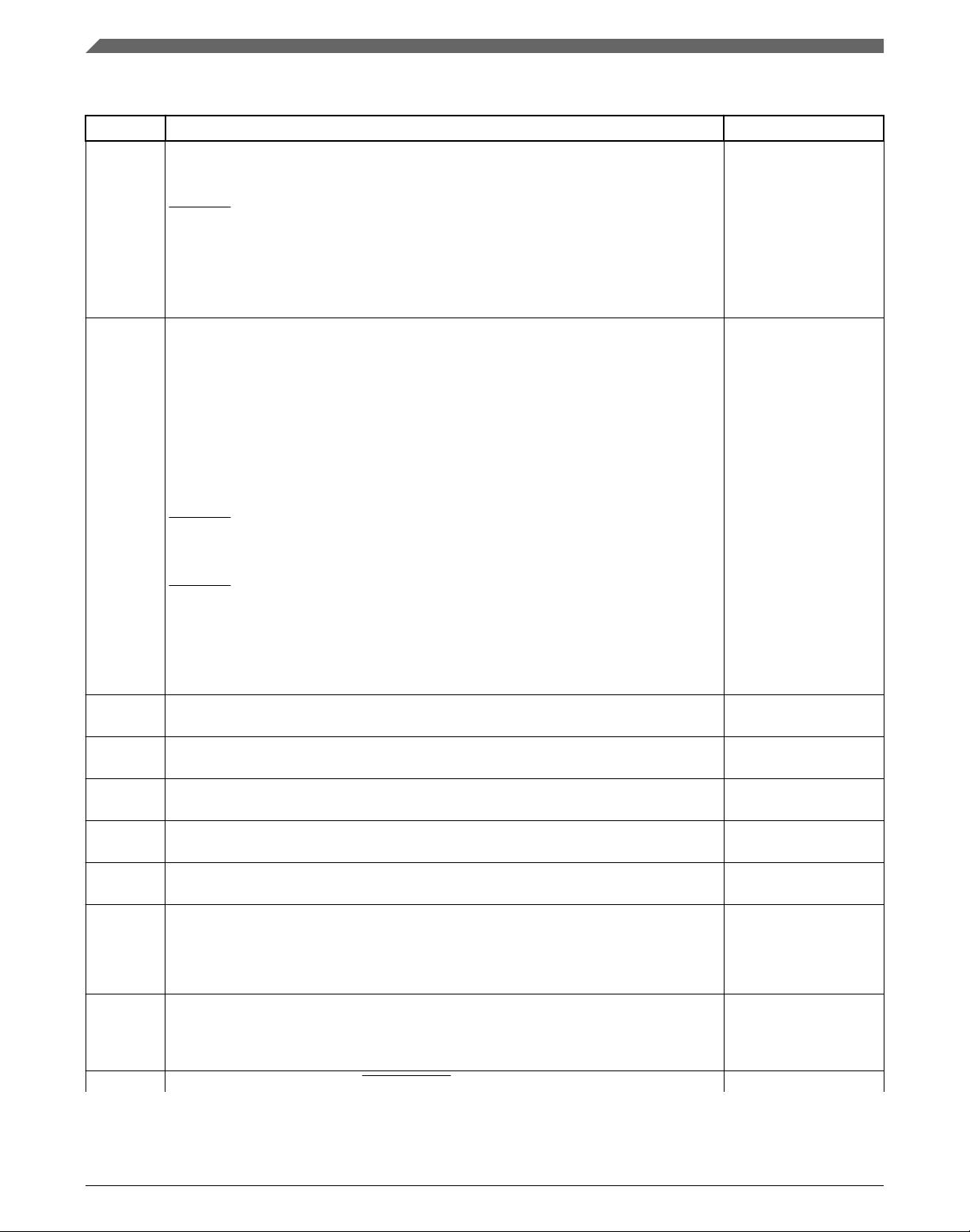

"Hardware and Layout Design Considerations for DDR4 SDRAM.pdf" 本文档主要讨论了DDR4 SDRAM在硬件设计和布局方面需要考虑的关键点和指南,适用于实施DDR4内存子系统的硬件工程师。文档中的规则和建议是板级设计师开始具体实施(如fly-by内存拓扑)的基础。特别提醒,设计者在制造电路板之前应使用仿真模型验证信号完整性、电气定时等所有方面。 推荐的资源包括: 1. 应用设备参考手册中的DDR章节 2. Micron公司的网站(http://www.micron.com) 3. JEDEC的网站(http://www.jedec.com,例如DDR4 SDRAM规范) 以下是文档的主要内容: 1. 文档简介:介绍了该文档的目的和适用范围,强调了在实际设计前进行仿真验证的重要性。 2. 推荐资源:列出了一些额外的、重要的参考资料来源,帮助设计师获取更多详细信息。 3. DDR4设计检查清单:可能包含了一系列设计DDR4内存系统时应考虑的关键点,例如时钟同步、数据路径设计、电源管理等。 4. 选择终端电阻:在DDR4系统中,正确选择和配置终端电阻对于信号完整性至关重要,这涉及到差分信号的匹配、反射控制以及阻抗匹配。 5. 避免VREF噪声:VREF是DDR4内存中的关键电压参考,其稳定性对数据读写精度有直接影响。设计时必须避免VREF噪声,确保信号质量。 6. 布局策略:良好的布局可以减少信号间的串扰,提高系统性能。可能包括电源和地平面的分割、信号线的布设、关键组件的位置等。 7. 时序和同步:DDR4的时序要求比DDR3更严格,设计师需要理解时钟延迟、数据有效窗口、预充电周期等概念,以确保正确操作。 8. 电源管理:DDR4引入了新的电源管理功能,如低电压工作和动态电压与频率调整,需要在硬件设计中充分考虑。 9. EMI/EMC控制:为了满足电磁兼容性标准,设计中应考虑屏蔽、滤波和接地策略。 10. 测试和调试:提供了测试接口和调试方法的建议,以便在设计完成后验证系统功能和性能。 这份文档为DDR4 SDRAM的硬件设计和布局提供了一套全面的指导原则,旨在帮助工程师们避免常见问题,实现高效、可靠的内存系统设计。

剩余25页未读,继续阅读

- 粉丝: 2923

- 资源: 7737

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- C语言快速排序算法的实现与应用

- KityFormula 编辑器压缩包功能解析

- 离线搭建Kubernetes 1.17.0集群教程与资源包分享

- Java毕业设计教学平台完整教程与源码

- 综合数据集汇总:浏览记录与市场研究分析

- STM32智能家居控制系统:创新设计与无线通讯

- 深入浅出C++20标准:四大新特性解析

- Real-ESRGAN: 开源项目提升图像超分辨率技术

- 植物大战僵尸杂交版v2.0.88:新元素新挑战

- 掌握数据分析核心模型,预测未来不是梦

- Android平台蓝牙HC-06/08模块数据交互技巧

- Python源码分享:计算100至200之间的所有素数

- 免费视频修复利器:Digital Video Repair

- Chrome浏览器新版本Adblock Plus插件发布

- GifSplitter:Linux下GIF转BMP的核心工具

- Vue.js开发教程:全面学习资源指南

信息提交成功

信息提交成功