数字集成电路:伪NMOS逻辑设计与性能分析

需积分: 5 126 浏览量

更新于2024-07-16

收藏 1.67MB PDF 举报

"第6章组合逻辑课件(2)2004年10月27日"

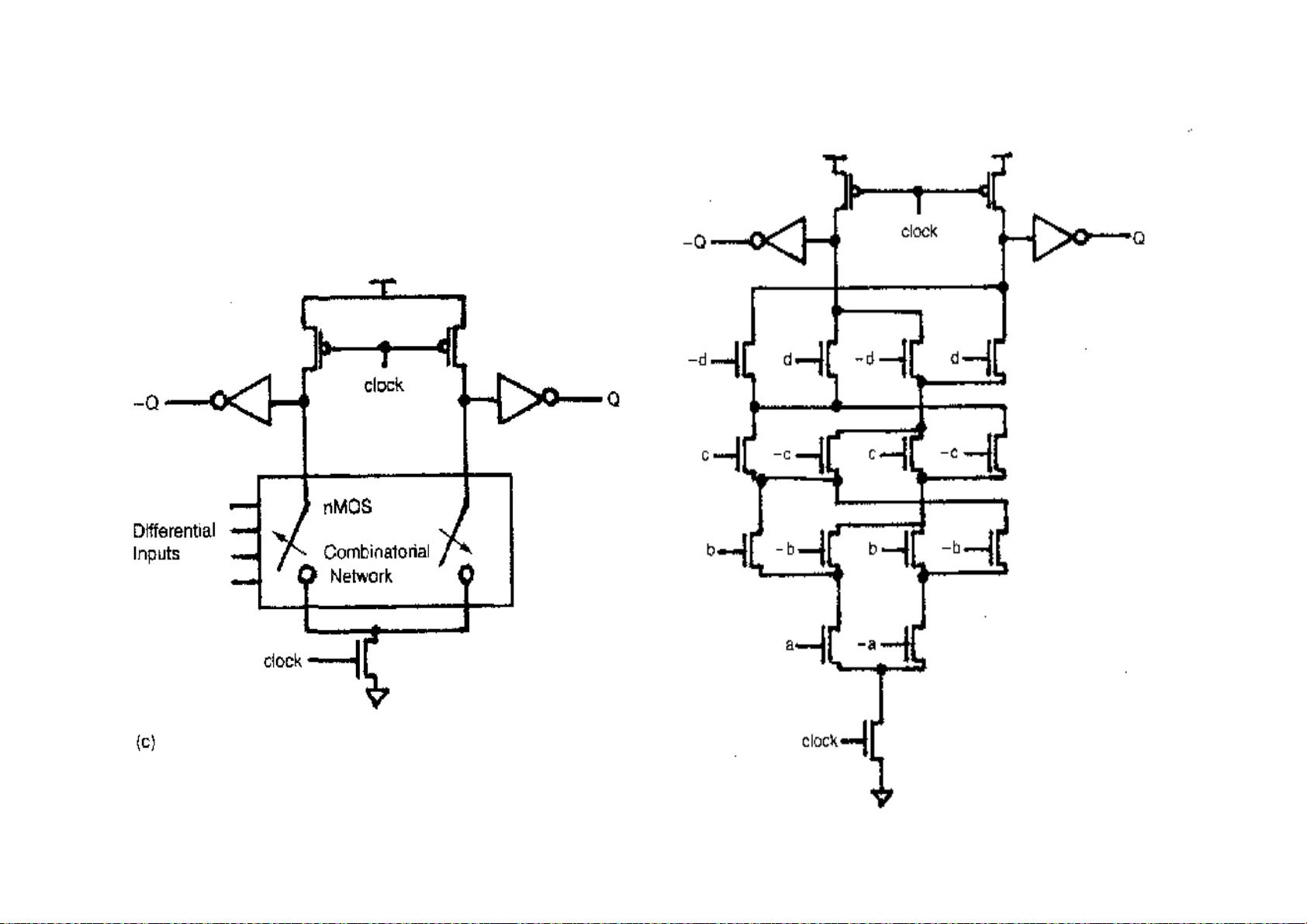

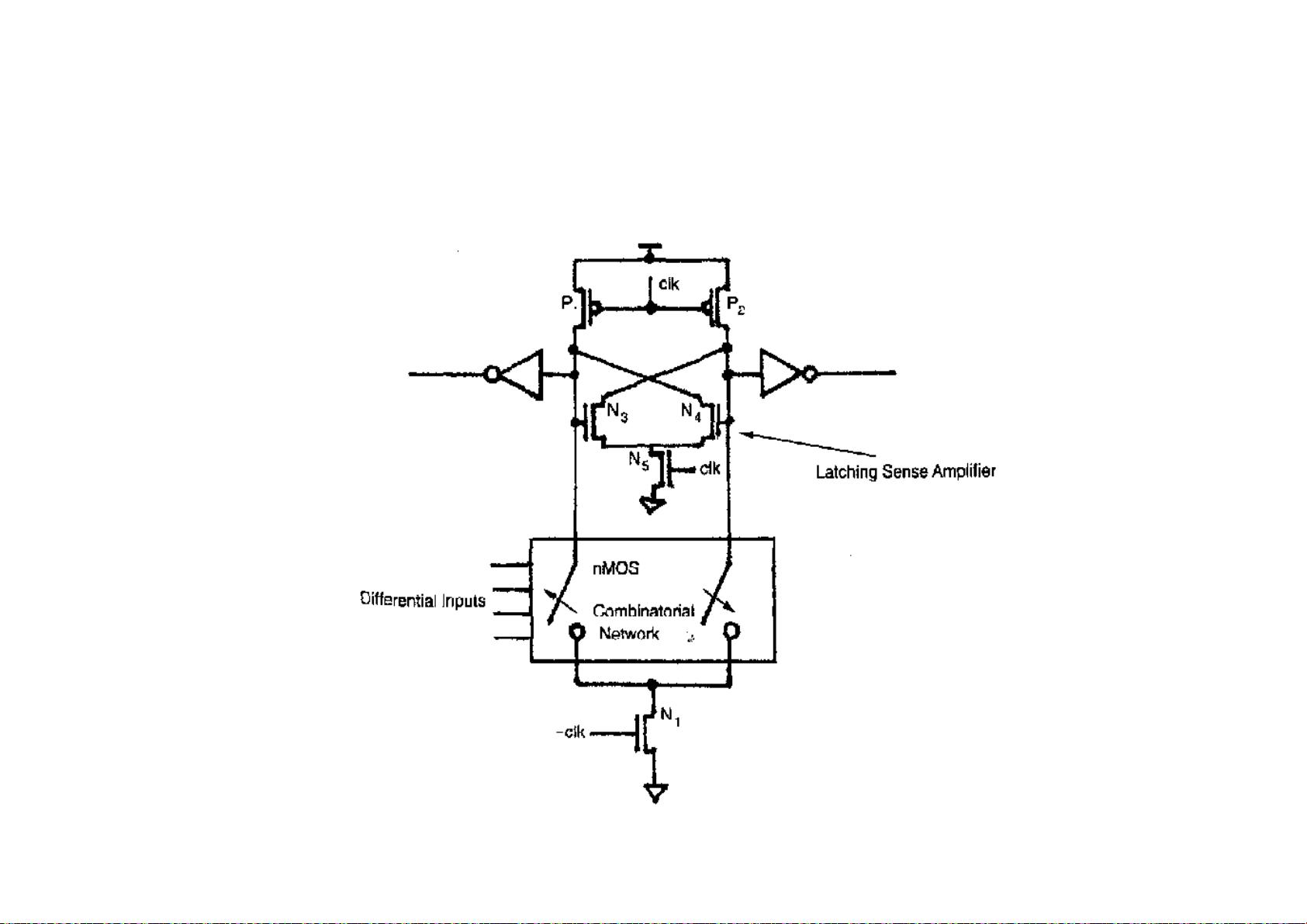

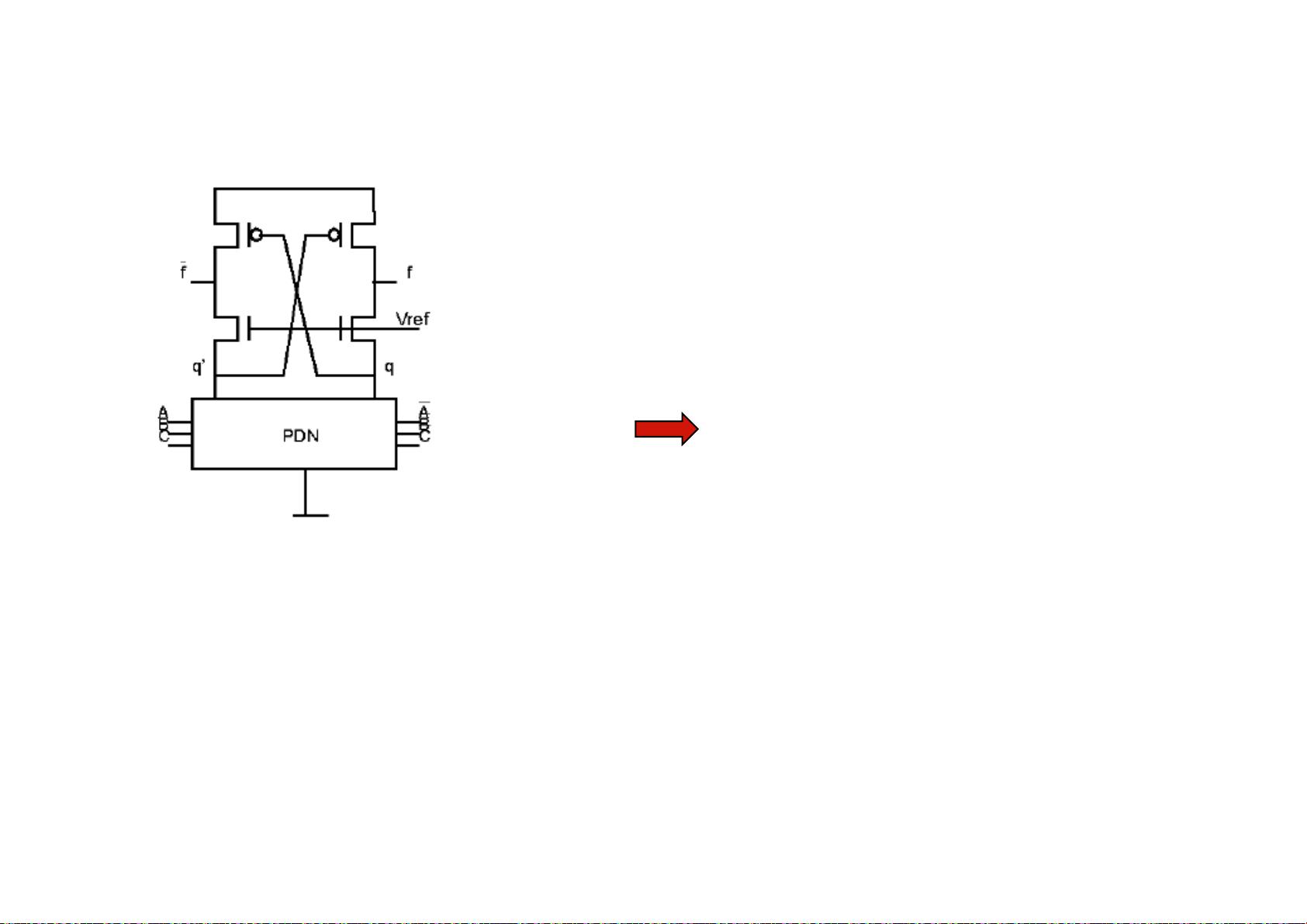

在这一节的组合逻辑课程中,主要讲解了关于数字大规模集成电路(VLSI)中的有比逻辑(Static CMOS Logic)及其变种——伪NMOS逻辑。有比逻辑是一种基于CMOS技术的电路设计,它主要由N个晶体管和负载组成,其中负载可以是电阻、耗尽型NMOS或PMOS。

在第1页中,提到了三种不同的负载类型:电阻负载、耗尽型NMOS负载和伪NMOS负载。电阻负载是最基本的形式,而耗尽型NMOS负载和伪NMOS负载则旨在优化电路性能。耗尽型NMOS负载允许VOL(低电平输出电压)接近VSS,但可能导致静态功耗。伪NMOS逻辑的设计目的是通过减少晶体管数量来减小电路面积,同时保持与互补CMOS相似的电压传输特性。

第2页进一步讨论了有比逻辑的特点。当使用电阻负载时,电路的输出电压VOH等于电源电压VDD,而VOL取决于负载电阻RL和晶体管的电容CL。这种电路的响应时间tpL与RL和CL有关,并且存在静态功耗,因为电流会流经负载电阻。

第3页介绍了伪NMOS逻辑的优势和缺点。它在保持输出特性类似于互补CMOS的同时,减少了所需的晶体管数量,从而缩小了电路面积。然而,代价是产生了静态功耗。伪NMOS逻辑的电压传输特性(VTC)展示了不同宽度/长度比例的PMOS负载对电路性能的影响,这通常需要在速度、功耗和噪声容限之间进行权衡。

第4页展示了一个伪NMOS电压传输特性的图表,显示了随着输入电压Vin的变化,输出电压Vout的变化情况。这个图表强调了不同晶体管尺寸如何影响电路的响应,以及如何在性能和功耗之间做出选择。

这些课件深入探讨了组合逻辑中用于提高集成度和优化性能的不同方法,特别是有比逻辑和伪NMOS逻辑的设计原理和优缺点。这些知识对于理解和设计现代数字集成电路至关重要。

2019-12-17 上传

2022-06-18 上传

2022-11-19 上传

2022-06-17 上传

2022-07-09 上传

壹零捌

- 粉丝: 226

- 资源: 101

最新资源

- api_training

- zentroo

- reveal-minimal:将Reveal.js与npm,Browserify,Jade等结合使用的最小设置

- node-978-1-7839-8448-0:使用 Redis 和 Node.js 构建可扩展的应用程序

- LogInApp:路线2.3

- mysql5.7.19_32.zip

- Raspberry_Pi_Weather_Station_WebUI:RpI气象站的Web UI

- certificates

- 12位AD转换芯片AD5621(stm32普通IO口SPI控制)

- 哈希表

- python_data_science

- ADF4002-数采板+电路+STM32+STC51,MSP430驱动_V0.2.zip

- 行业-文旅产业项目定位及运营策略.rar

- 传输线:传输线的基本模拟。-matlab开发

- 2020最新!5张VUE知识脑图,免费下载,最新分享!

- data:基于Google趋势数据的瑞士经济指标