同步静态随机访问存储器(SSRAM)技术解析

需积分: 9 5 浏览量

更新于2024-09-11

收藏 38KB PDF 举报

"SSRAM datasheet提供了关于同步静态随机访问存储器(Synchronous Static Random Access Memory)的详细信息,包括其内部结构、操作模式以及与传统SRAM的区别。文档中包含了多个SSRAM的时序图,展示了其工作原理。"

同步静态随机访问存储器(SSRAM)是一种特殊的SRAM类型,它在保持传统SRAM内部使用锁存器的同时,引入了同步的接口来处理控制、地址和数据信号。与传统的异步SRAM不同,SSRAM通过同步时钟信号来同步外部的输入和内部的操作。

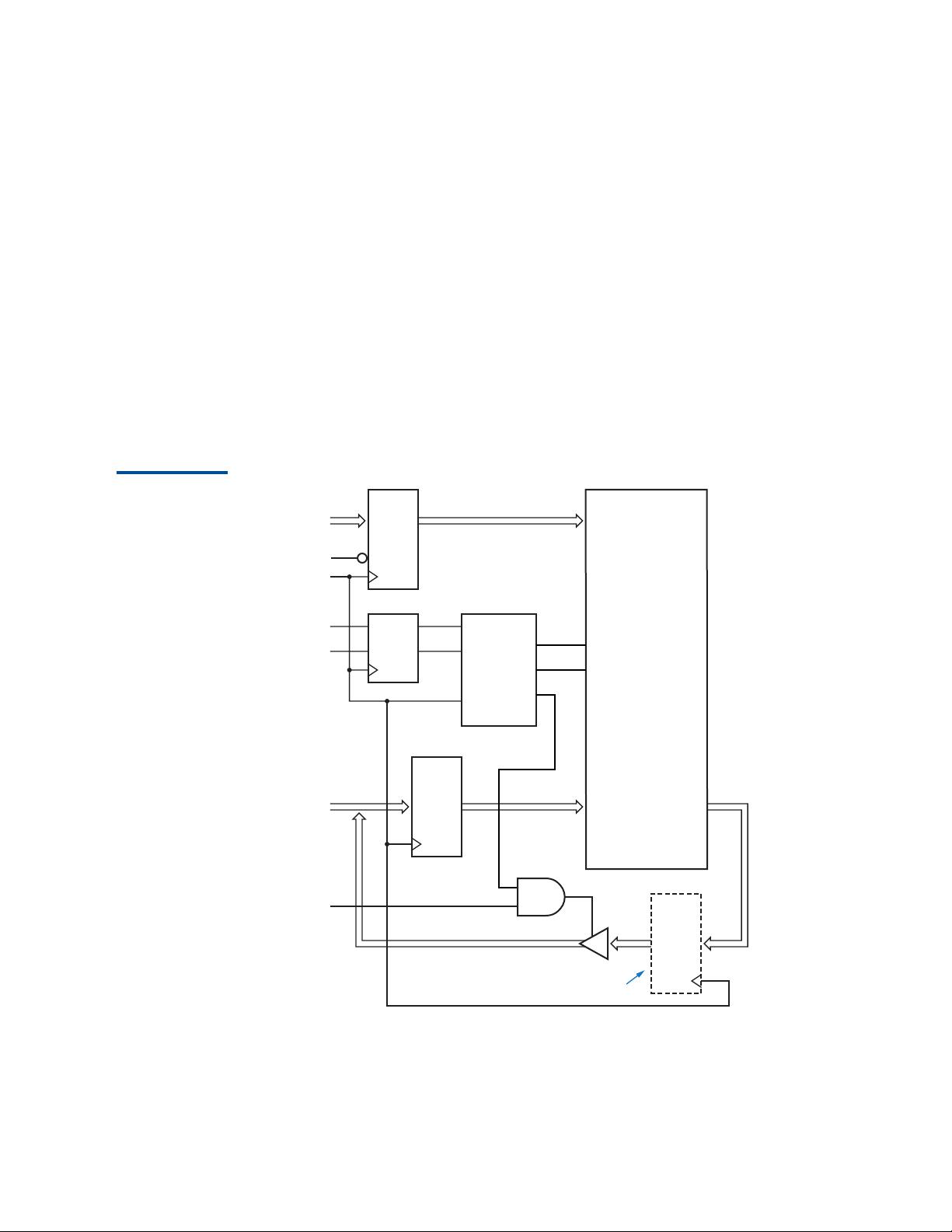

如图10-26所示,SSRAM的关键改进在于用边沿触发的寄存器AREG和CREG替代了内部地址和控制信号路径上的锁存器。这样,在时钟的上升沿到来之前设置的操作会在随后的时钟周期内由内部执行。对于写操作,输入数据由INREG寄存器捕获;而对于读操作,根据设备是采用"流水线"输出还是"直通"输出,可能会提供或不提供OUTREG寄存器来暂存读取的数据。

其中,早期的SSRAM类型是晚写SSRAM,具有直通输出特性。在读取操作(如图10-27(a)所示)中,控制和地址输入在时钟上升沿被采样,然后SSRAM阵列开始访问并返回数据。读操作完成后,数据通过DOUT端口即时输出。

SSRAM的这种设计使得数据传输与时钟同步,提高了系统的整体性能,因为它消除了异步操作可能导致的延迟不确定性。此外,由于控制信号和地址信号是在时钟边沿采样,因此可以更精确地控制操作的开始和结束,这在高速系统中尤其重要。

SSRAM的时序图展示了不同的操作模式(如读、写)与时钟脉冲之间的关系,这些图对于理解和设计使用SSRAM的系统至关重要。理解这些时序图,工程师可以确保系统与SSRAM的接口正确地按照其规定的时间参数工作,从而避免数据丢失或错误。

SSRAM datasheet是了解和应用SSRAM技术的重要参考资料,它详细阐述了SSRAM的工作机制、操作流程以及关键的时序特性,对于设计高性能的存储系统具有极高的价值。

118 浏览量

2022-09-21 上传

2022-09-20 上传

2012-12-27 上传

107 浏览量

2022-09-14 上传

2024-01-15 上传

leeshuenngi

- 粉丝: 1

最新资源

- 昆仑通态MCGS嵌入版_XMTJ温度巡检仪软件包解压教程

- MultiBaC:掌握单次与多次组批处理校正技术

- 俄罗斯方块C/C++源代码及开发环境文件分享

- 打造Android跳动频谱显示应用

- VC++实现图片处理的小波变换方法

- 商城产品图片放大镜效果的实现与用户体验提升

- 全新发布:jQuery EasyUI 1.5.5中文API及开发工具包

- MATLAB卡尔曼滤波运动目标检测源代码及数据集

- DoxiePHP:一个PHP开发者的辅助工具

- 200mW 6MHz小功率调幅发射机设计与仿真

- SSD7课程练习10答案解析

- 机器人原理的MATLAB仿真实现

- Chromium 80.0.3958.0版本发布,Chrome工程版新功能体验

- Python实现的贵金属追踪工具Goldbug介绍

- Silverlight开源文件上传工具应用与介绍

- 简化瀑布流组件实现与应用示例