JPEG2000 5/3小波变换FPGA实现与优化

136 浏览量

更新于2024-09-02

收藏 265KB PDF 举报

"JPEG2000中5/3离散小波多层变换的FPGA实现,通过VLSI设计结构优化,采用移位-相加替代卷积,使用双端口RAM和地址生成模块,实现了高效高速的二维三层小波变换硬件平台。"

在图像压缩领域,JPEG2000作为一种先进的国际标准,相较于传统的JPEG标准,它提供了更高的压缩效率、无损和有损压缩的灵活性、分辨率渐进传输以及感兴趣区域编码等功能。JPEG2000的核心技术之一是离散小波变换(DWT),而5/3小波滤波器因其优良的性能被推荐用于无损压缩。

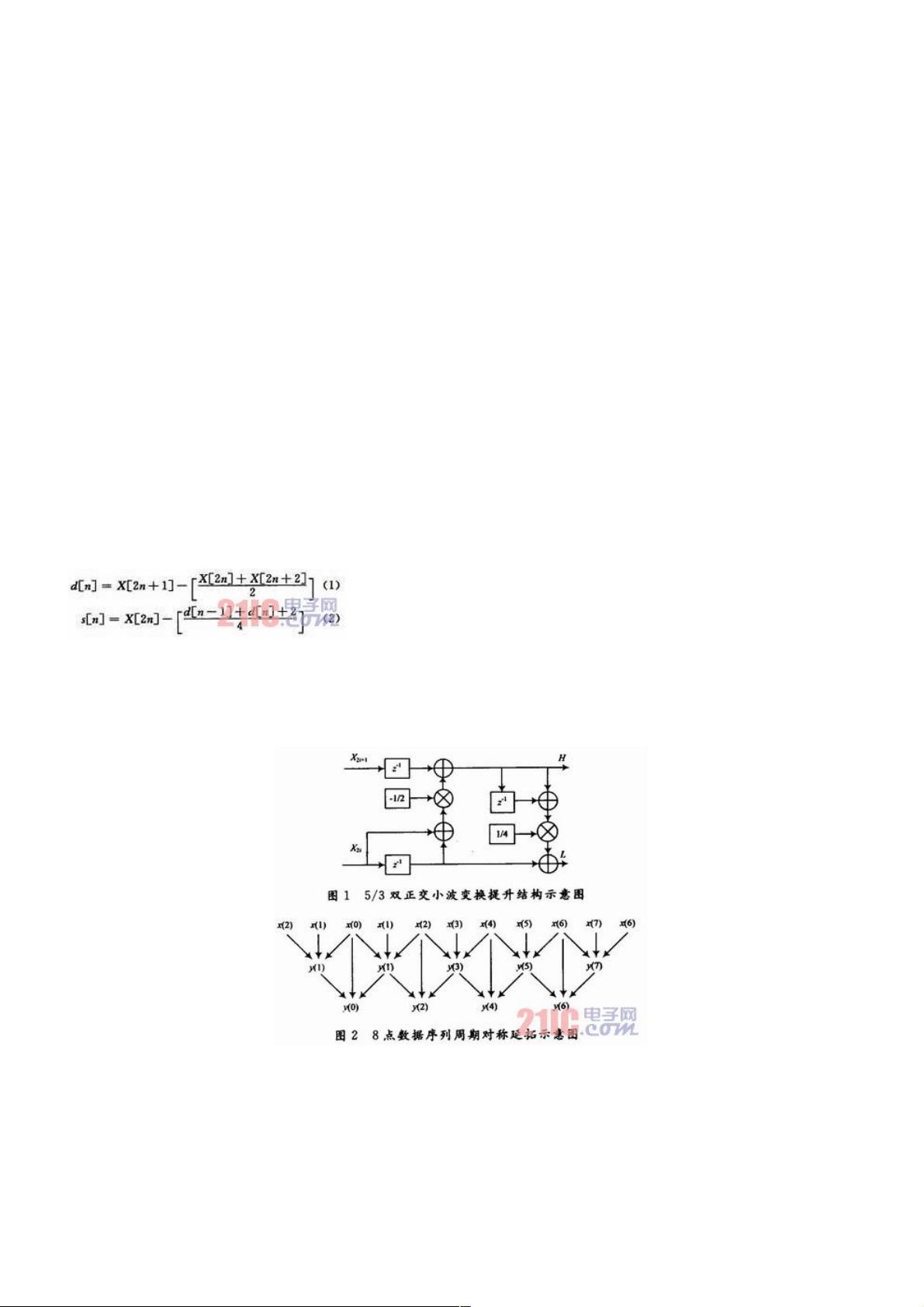

本文关注的是JPEG2000中5/3小波变换的硬件实现,特别在FPGA(Field-Programmable Gate Array)平台上。传统的DWT计算通常涉及复杂的卷积运算,这在硬件实现时需要大量计算资源。为解决这一问题,论文采用了I. Daubechies和W. Sweldens提出的提升算法,该算法通过移位-相加操作替代了原本的卷积,显著减少了硬件实现的复杂度。

作者提出了一种创新的VLSI设计结构,该结构将数据的奇偶分裂和边界延拓操作集成到双端口RAM的地址生成单元中,无需额外的计算单元。这种设计优化了处理流程,减少了硬件需求。通过Verilog语言编写RTL(Register Transfer Level)级代码,进行了功能仿真,最终在FPGA上实现了这一设计,并达到了156 MHz的最高时钟频率,显示了优越的整体性能。

设计中,5/3小波变换采用两组一维变换,通过流水线技术提升了处理速度。在二维变换中,通过双端口RAM的调度执行小波变换的分裂和边界扩展,而不需要额外的模块,进一步提高了效率。这种方法不仅简化了硬件实现,还确保了高速和低延迟,适应了实时图像处理的需求。

这篇研究为JPEG2000的5/3离散小波变换提供了快速且高效的FPGA实现方案,对于推动JPEG2000在嵌入式系统和多媒体设备中的应用具有重要意义。该研究的创新点在于将数据处理和内存操作相结合,避免了额外的计算单元,使得硬件设计更加紧凑和高效,这对于资源受限的嵌入式环境尤其重要。

2021-07-13 上传

2020-10-19 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

2024-12-24 上传

2024-12-24 上传

weixin_38741101

- 粉丝: 6

- 资源: 926

最新资源

- RPMA回传+ Arduino Yun –第3部分-项目开发

- easy-redux:简化redux api

- BarreOutils:锻炼巴雷特迪尔斯

- copylight:jQuery 插件为内容许可证提供视觉强化

- 2021最新孜然导航系统 v1.0

- 微信小程序-小厨房

- visibl:通过React HOC进行视口内检测

- canvasinvaders:HTML Canvas 上的太空入侵者(有点)

- clickhousewriter.zip

- 西门子PLC工程实例源码第637期:转速PID控制程序(双脉冲).rar

- 洗剂

- 物理和云Cayenne交换机-项目开发

- fit-text-to-screen:

- CSYE6220:CSYE6220的分配

- ChatBot

- FJLRS:费·琼斯实验室请求系统