FPGA与ASIC设计:状态机与数据路径优化

需积分: 9 111 浏览量

更新于2024-07-30

收藏 783KB PDF 举报

"本资源主要探讨了在FPGA和ASIC设计中如何实现高性能数字系统,特别关注了状态机和数据路径的设计与优化。状态机作为复杂逻辑控制的核心,对于系统的性能和可靠性至关重要。内容涵盖了状态机的基础知识,包括分类、结构、编码和优化设计,并通过Verilog硬件描述语言进行实例演示。此外,还讨论了数据路径的设计规则、时间调度、路径优化以及与状态控制单元的协调。"

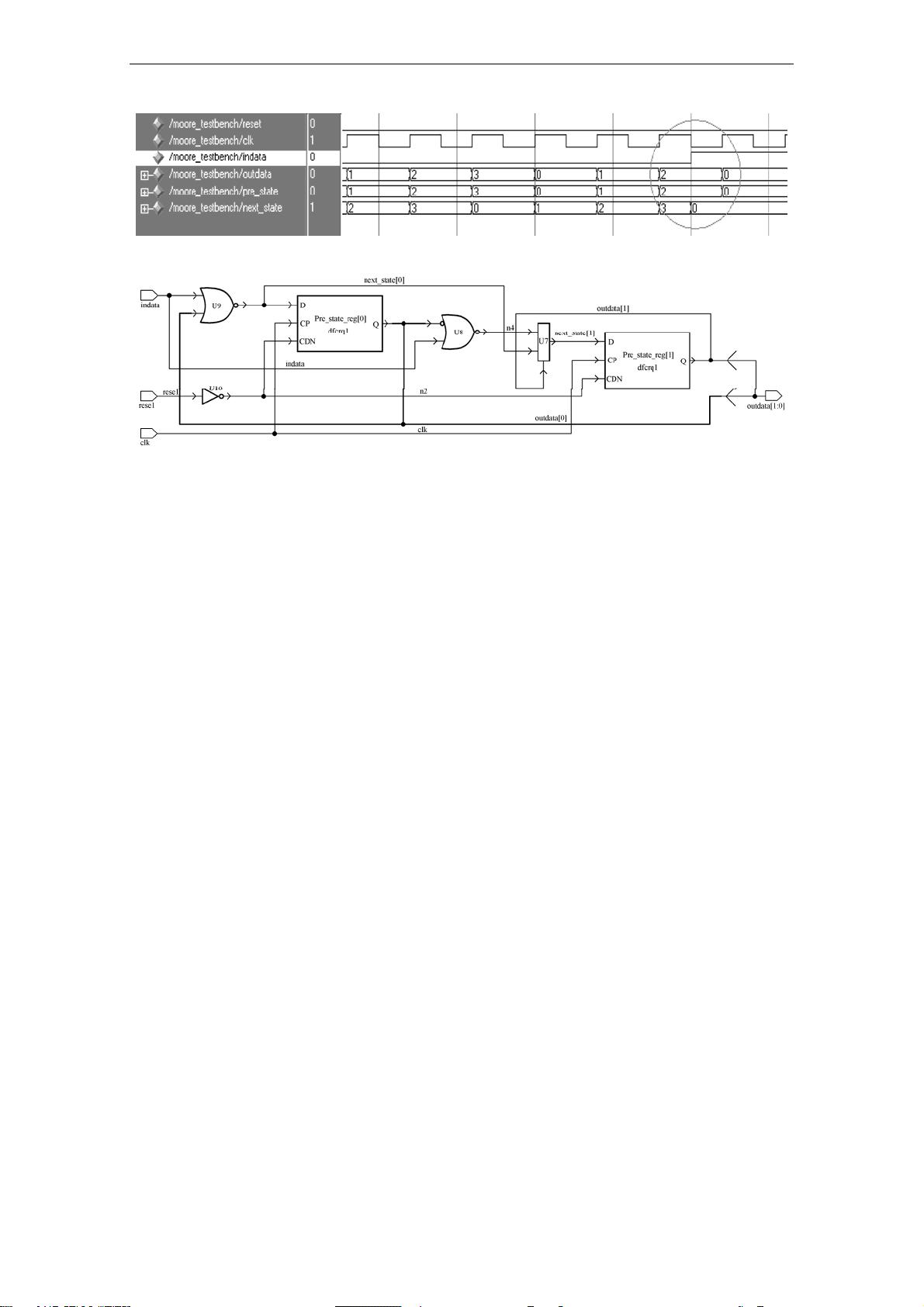

在现代数字系统设计中,状态机扮演着关键角色,尤其是在FPGA和ASIC这样的硬件实现中。状态机是一种数学模型,用于描述具有有限数量离散状态及其转换的系统行为。状态机由状态和转移组成,每个状态都有独特的名称(或匿名),并且可能伴随着进入和退出时执行的操作。内部转移则指在状态内部发生的活动,而不改变当前状态。

状态机的分类主要包括 Moore状态机 和 Mealy状态机。Moore状态机的输出只取决于当前状态,而Mealy状态机的输出同时依赖于当前状态和输入。状态机的结构通常包括状态寄存器、状态编码、状态转移逻辑和输出逻辑。状态编码是将每个状态映射到二进制编码的过程,可以影响硬件的面积和速度。优化设计旨在减少状态机的复杂性,提高效率。

Verilog作为一种高级硬件描述语言,是实现状态机的理想工具。通过Verilog,设计者可以清晰地定义状态机的行为,并进行功能验证,确保其符合设计需求。状态机的物理实现受益于这种形式化的描述,因为它允许更精确的逻辑综合和仿真。

数据路径设计是另一个关键点,它涉及到系统的计算能力。设计规则指导如何构建数据通路,时间调度和分配则确保系统能在规定的时间内完成操作。路径优化旨在减少延迟,提高吞吐量,而状态控制单元与数据路径的分割是设计高效系统的策略之一,确保控制逻辑和计算逻辑的分离,以实现更好的性能。

本资源深入讲解了状态机和数据路径设计的各个方面,对于理解和实现高性能、高可靠性的FPGA和ASIC数字系统具有重要价值。无论是初学者还是经验丰富的工程师,都能从中获得关于如何优化数字系统设计的宝贵知识。

2021-01-13 上传

2021-05-20 上传

2022-07-14 上传

2022-09-19 上传

2022-07-15 上传

2021-10-01 上传

2021-09-30 上传

hsx0709

- 粉丝: 0

- 资源: 2

最新资源

- 温特线性matlab代码-matlab_NS_solvers:旧的研究代码。主要是涡量公式中的2DNS求解器

- 行业文档-设计装置-一种切纸机的双位刀头.zip

- Lora-32-Connect-by-Wifi

- 视图:场景模块的界面,为发送到渲染器的显示对象提供用户交互输入输出和剔除管理

- omniauth-rails_csrf_protection:在Rails应用程序的OmniAuth请求端点上提供CSRF保护

- ryanatkn

- 基于神经网络的人脸识别.zip

- derrobott.github.io:没事了

- matlab导弹落点代码-missile_simulation_matlab:导弹仿真Matlab代码

- iains:TestAccount

- xlog:xlog是netcontext感知HTTP应用程序的记录器

- 自动驾驶汽车案例研究

- 「基于图像识别的收银台」客户端软件,基于OpenCV + Qt,需要搭配「基于图像识别的收银台」后端服务使用。.zip

- darwish-rainmeter

- CSCI3800_Sp15_Team8:CSCI3800 Spring 2015 Team 8项目

- blog