Verilog HDL建模秘籍:从入门到精通

需积分: 16 65 浏览量

更新于2024-07-26

收藏 19.53MB PDF 举报

"Verilog那些事——深入探讨Verilog HDL的建模技术"

在电子设计自动化(EDA)领域,Verilog HDL是一种广泛使用的硬件描述语言,用于创建数字系统的模型,特别是针对Field-Programmable Gate Array (FPGA)和Application-Specific Integrated Circuit (ASIC)的设计。"Verilog那些事"这个主题旨在揭示Verilog HDL建模的重要性,并为初学者提供指导,以克服学习过程中的困难。

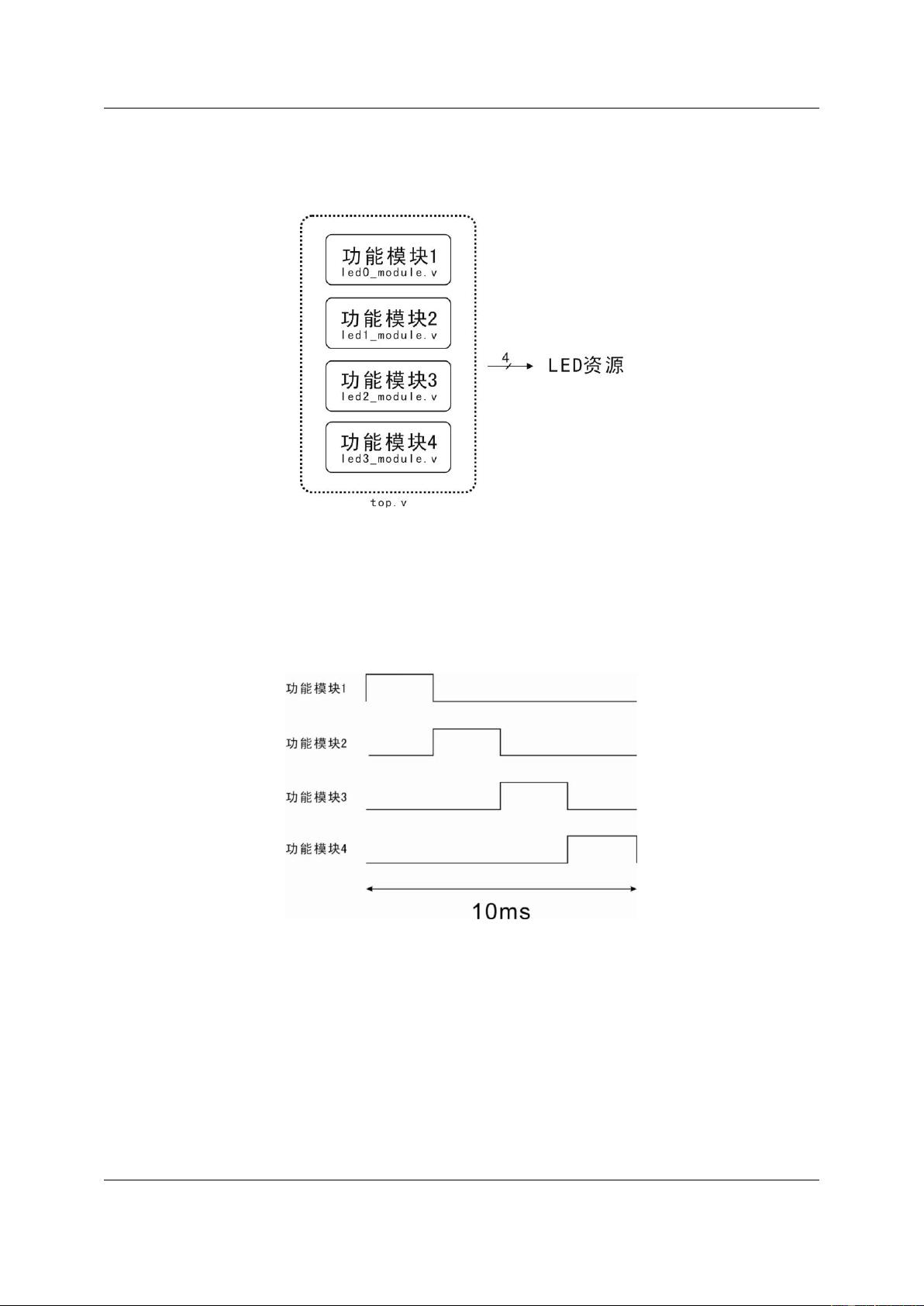

建模是Verilog HDL的核心概念,它允许设计者以模块化的方式描述复杂的逻辑电路。就像用乐高积木构建结构一样,FPGA的设计者利用Verilog HDL的模块化特性,将小的逻辑单元组合成大型系统。建模不仅仅是简单的模块建立,它还涉及到如何有效地组织和表示设计的结构,以便于理解和实现。

在学习Verilog HDL的过程中,许多初学者可能会遇到理解上的困扰,这是因为缺乏对建模方法和技巧的掌握。"建模篇"可能包含了作者对于如何规划和构建清晰、有组织的Verilog HDL模型的见解和建议。作者强调,良好的建模技巧不仅可以使设计者自己更好地理解设计,也能让其他人更容易地阅读和复用代码。

网络上建议学习Verilog HDL时要多参考他人代码,但如果没有理解建模的基础,这可能变成一种痛苦的经历。作者引用了一句名言,暗示阅读他人代码有时如同在忍受折磨,因为没有建模技巧的人很难理解别人的思维过程。因此,掌握建模技巧至关重要,这不仅关乎个人的理解,也关系到代码的可读性和团队协作的效率。

时序分析和功能仿真虽然也是Verilog HDL设计中不可或缺的部分,但在初期,建模技巧的培养可能更为关键,因为它奠定了整个设计的基础。作者坚信,一旦掌握了建模的艺术,Verilog HDL的表现力甚至可以超过其他高级编程语言。

对于那些在Verilog HDL和FPGA学习道路上感到迷茫的初学者,作者分享了自己的建模经验,希望能帮助他们跨越学习障碍,提升建模能力,从而更顺利地进行FPGA设计。这本笔记很可能包含了一系列实用的建模策略和案例,以帮助读者构建清晰、结构化的Verilog HDL模型,从而在设计过程中取得更大的成功。

2021-04-13 上传

2019-04-16 上传

2011-07-11 上传

u010442980

- 粉丝: 0

- 资源: 1

最新资源

- MATLAB全常用函数下载,权威性

- 基于C#的 office owc统计图解决方案

- 关于modbus学习的 pdf 文档

- 微软的面试题及答案-超变态但是很经典

- CISCO交换机配置AAA、802.1X以及VACL

- microsoft office excel 2003 函数应用完全手册

- ModBus通讯协议

- 学员信息管理系统PPT答辩稿

- D-LINK校园网设计

- 计算机三级等级考试资料

- 嵌入式C C++语言精华应用

- Java23种设计模式

- java和jsp编程常见到的异常解决方案

- Linux操作系统下C语言编程入门.pdf

- Wrox.Beginning.Shell.Scripting.Apr.2005.eBook-DDU.pdf

- 基于MVC模式Struts框架