DDR控制器:支持DDR2与ECC特性详解

需积分: 9 69 浏览量

更新于2024-07-21

收藏 1.94MB DOC 举报

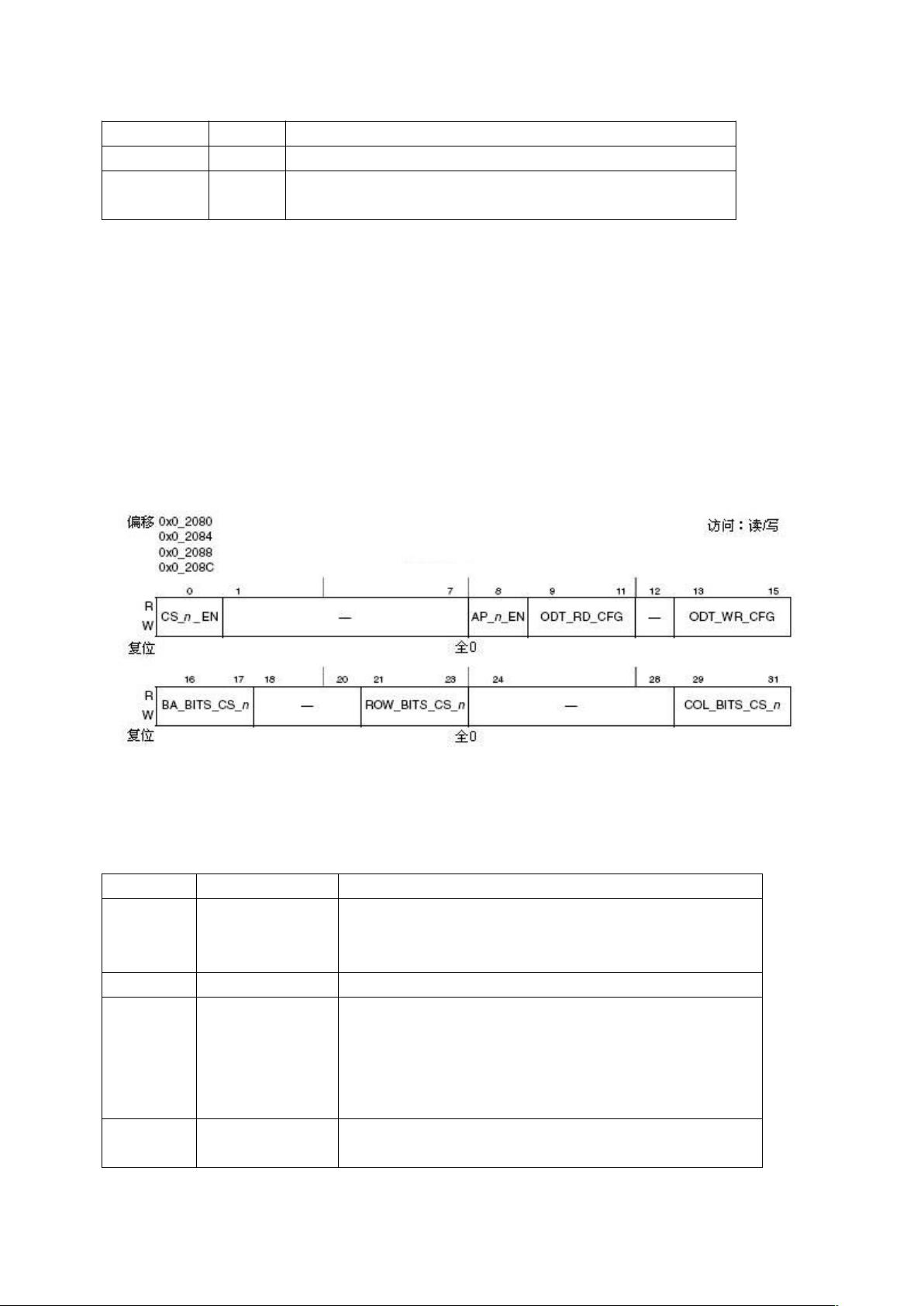

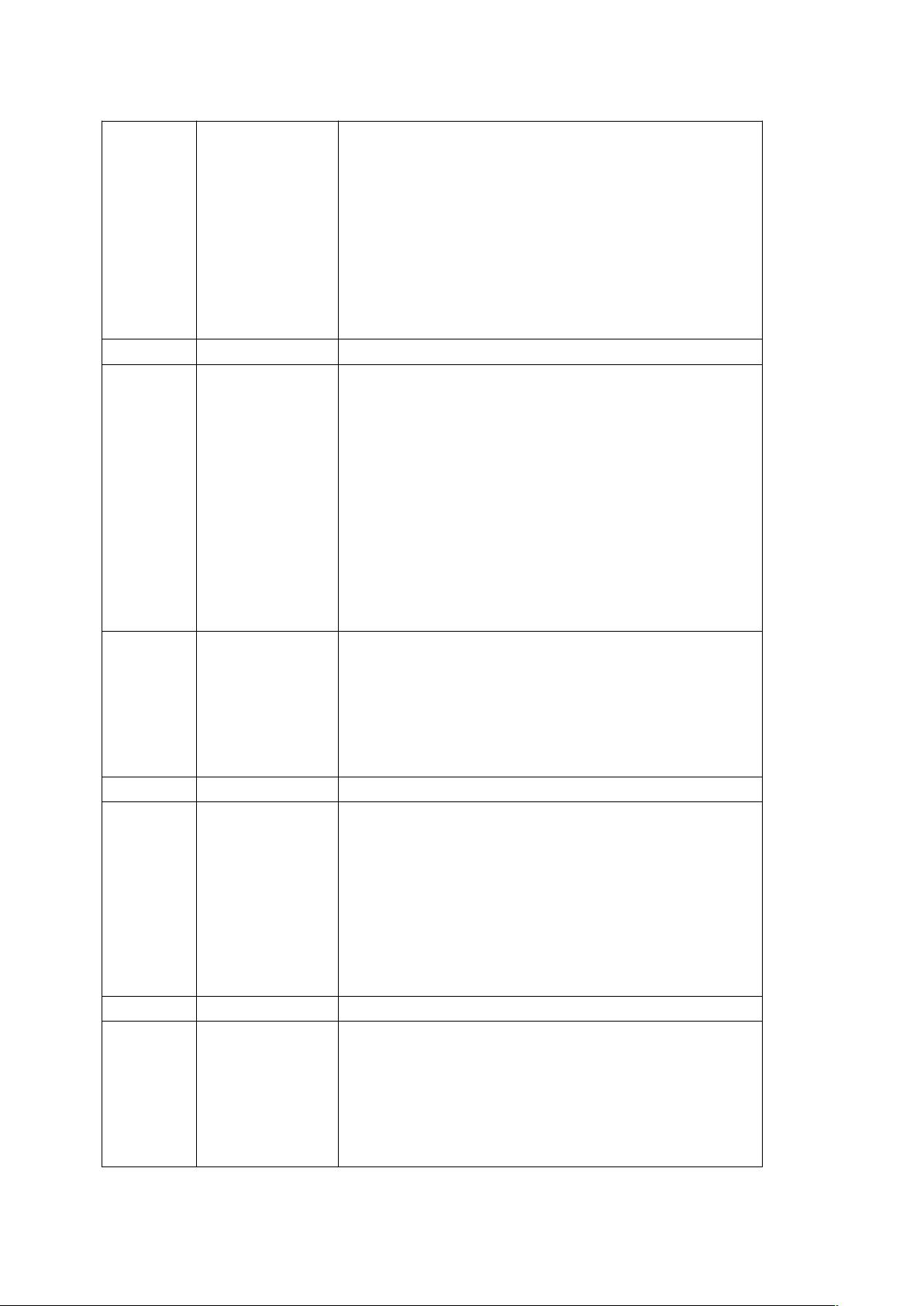

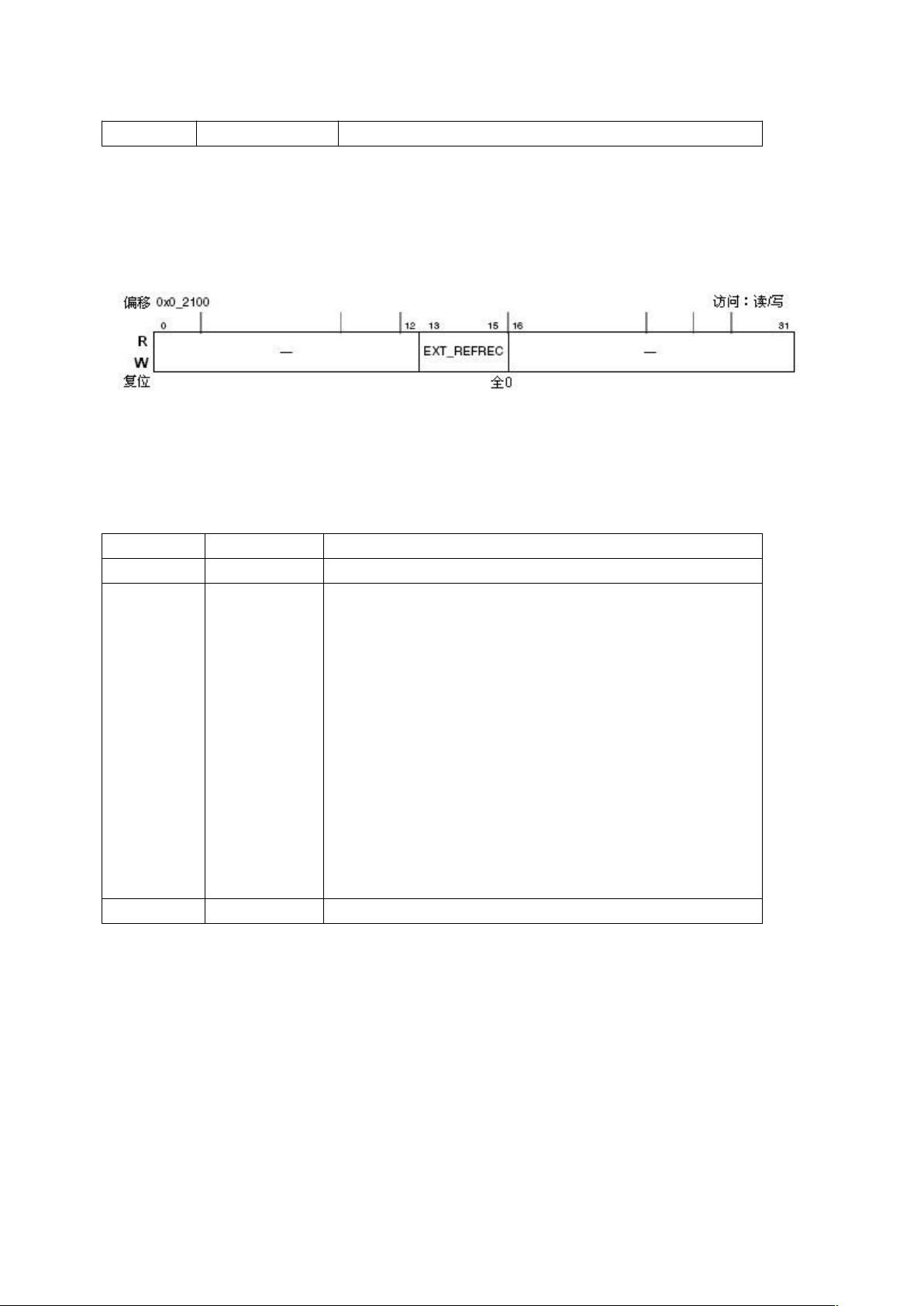

第9章 "DDR存贮器控制器"深入讲解了现代计算机系统中用于管理高速同步动态随机存取内存(DDR SDRAM)的关键组件。这一章节主要关注于一种完全可编程的控制器,它能够支持多种第一代JEDEC标准下的x8或x16 DDR和DDR2内存,涵盖了非缓存式和寄存式双列直插内存模块(DIMM)。然而,控制器设计有一个限制,即不支持在同一系统中混用不同类型的内存或者非缓存式与寄存式DIMM。

控制器的核心特性包括:

1. 内存兼容性:支持DDR和DDR2 SDRAM,具备64/72位宽的数据总线,分别对应这两种内存的不同数据宽度要求。

2. 可编程定时参数:允许用户根据SDRAM的具体规格调整各种定时参数,以优化性能和功耗。

3. 内存配置:提供四个独立寻址的物理存贮体,支持不同容量设备(如64M到4G位),尽管没有直接的x4数据端口。

4. 内存类型支持:兼容非缓存式和寄存式DIMM,以及芯片选择的交叉支持,确保内存模块间的灵活连接。

5. ECC纠错技术:采用两位差错检测和一位差错恢复的ECC,提供8位校验字来检测并纠正64位数据,保证数据的准确性。

6. 高效请求处理:内置四表项输入请求队列,有助于提高内存访问效率。

7. 内存管理:支持打开页面管理,每个逻辑存贮体都有独立的表项,便于有效管理内存空间。

8. 自动初始化:控制器能自动进行DRAM初始化,或在软件控制下进行,简化系统设置。

9. 电源管理:支持动态电源管理,降低空闲时的功耗,并能在两倍SDRAM时钟频率下工作,支持睡眠电源管理。

10. 错误注入:用于测试和调试,允许开发者在系统运行时模拟错误情况。

此外,控制器还支持两种操作模式:动态电源管理模式和自动预充电模式。前者通过在数据事务间断开时关闭CKE信号来节省电力,而后者在每次读写事务后自动预充电,确保内存的持续可用性。

图9-1展示了DDR存贮器控制器的基本架构图,详细的控制器功能描述可在9.5节中找到。掌握这些知识点对于理解现代计算机系统中内存控制器的高效运作至关重要,特别是在设计高性能和可靠性的系统时。

172 浏览量

2013-03-07 上传

2022-09-20 上传

2009-05-11 上传

269 浏览量

2015-05-16 上传

2010-03-15 上传

2022-07-14 上传

2023-08-13 上传

jlushengming

- 粉丝: 5

- 资源: 29

最新资源

- BottleJS快速入门:演示JavaScript依赖注入优势

- vConsole插件使用教程:输出与复制日志文件

- Node.js v12.7.0版本发布 - 适合高性能Web服务器与网络应用

- Android中实现图片的双指和双击缩放功能

- Anum Pinki英语至乌尔都语开源词典:23000词汇会话

- 三菱电机SLIMDIP智能功率模块在变频洗衣机的应用分析

- 用JavaScript实现的剪刀石头布游戏指南

- Node.js v12.22.1版发布 - 跨平台JavaScript环境新选择

- Infix修复发布:探索新的中缀处理方式

- 罕见疾病酶替代疗法药物非临床研究指导原则报告

- Node.js v10.20.0 版本发布,性能卓越的服务器端JavaScript

- hap-java-client:Java实现的HAP客户端库解析

- Shreyas Satish的GitHub博客自动化静态站点技术解析

- vtomole个人博客网站建设与维护经验分享

- MEAN.JS全栈解决方案:打造MongoDB、Express、AngularJS和Node.js应用

- 东南大学网络空间安全学院复试代码解析