H.264/FRExt在嵌入式系统/ARM技术中的应用解析

49 浏览量

更新于2024-09-01

收藏 326KB PDF 举报

"嵌入式系统/ARM技术中的H.264 FRExt技术实现和运用"

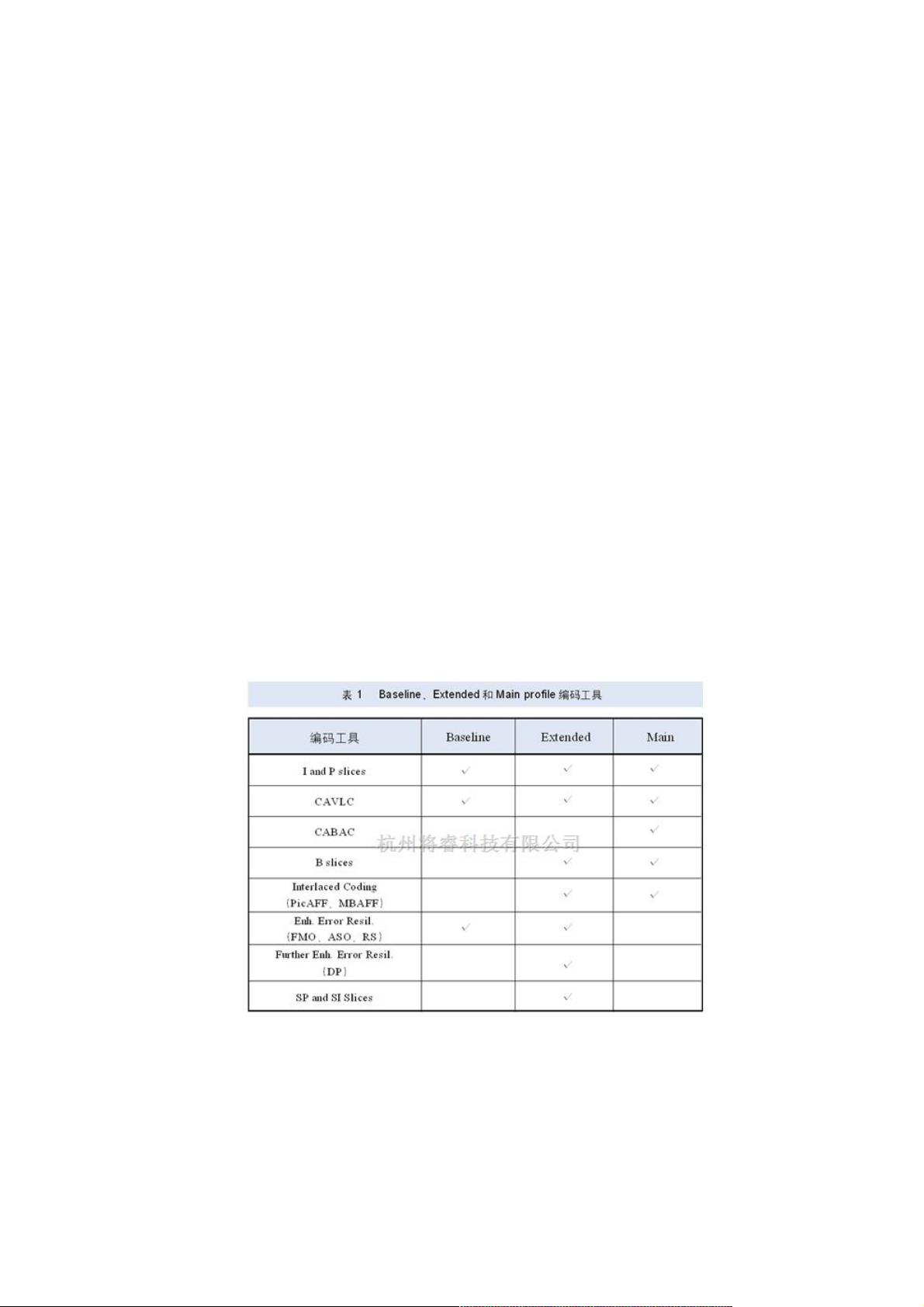

H.264,也称为AVC (Advanced Video Coding),是国际电信联盟(ITU-T)与国际标准化组织(ISO/IEC)联合制定的一种高效视频编码标准,它的出现大大提升了视频压缩效率,降低了带宽需求,适用于各种多媒体应用,包括高清电视、网络流媒体、移动设备等。H.264的发展源自早期的H.26L项目,其标准制定工作由联合视频团队(Joint Video Team, JVT)完成,涵盖了Baseline Profile、Extended Profile和Main Profile等多个级别,每种Profile包含了不同的编码工具,以满足不同应用场景的需求。

H.264的核心技术包括熵编码、块运动估计和补偿、预测编码、变换编码以及自适应量化等。其中,熵编码如上下文自适应二进制算术编码(CABAC)和上下文自适应变长编码(CAVLC)提高了编码效率;块运动估计和补偿技术则允许对帧间的相似性进行利用,减少冗余信息;预测编码通过分析相邻像素的值来预测当前像素,进一步减少数据量;变换编码将空间域的信号转换到频率域,便于压缩;自适应量化根据图像内容的重要性调整量化参数,保证视觉质量的同时减少码率。

FRExt(Fidelity Range Extensions)是H.264的一个扩展部分,于2004年完成,旨在提供更高的图像质量和增强功能。FRExt引入了支持高动态范围(HDR)视频、广色域(Wide Color Gamut)、多视点视频编码(Multi-View Video Coding, MVC)等特性,使得H.264不仅能满足传统标清和高清视频的编码,还能适应4K、8K超高清视频以及3D视频的编码需求。

在嵌入式系统,尤其是基于ARM架构的硬件平台上实现H.264编码和解码是一项挑战,因为这些平台通常资源有限。ARM处理器提供了高效的处理核心和各种硬件加速器,例如NEON SIMD(Single Instruction Multiple Data)单元,用于加速多媒体处理。通过优化算法和利用硬件加速功能,可以实现在嵌入式系统上的高效H.264编解码,从而在保持低功耗的同时提供流畅的视频体验。

为了在嵌入式系统中实现H.264 FRExt技术,开发者需要考虑以下几个关键点:

1. 选择合适的编码库:如OpenH264、FFmpeg等开源库,它们提供了对H.264和FRExt的支持,并且经过优化,适合在嵌入式平台运行。

2. 硬件加速器的利用:针对ARM处理器的特性,如使用NEON指令集进行并行计算,提高编码速度。

3. 动态内存管理:嵌入式系统内存有限,需要精心设计内存分配策略,避免内存浪费和泄露。

4. 能耗优化:在保证性能的同时,考虑降低功耗,如采用低功耗模式、智能调度等手段。

5. 验证和测试:在不同配置和场景下进行全面测试,确保编码解码的稳定性和兼容性。

H.264 FRExt技术在嵌入式系统/ARM技术中的实现是一项综合了编码理论、硬件优化和系统工程的复杂任务,需要开发者深入理解H.264标准,熟悉ARM处理器的特性和优化技巧,才能有效地将这一先进视频编码技术应用于实际产品中。

146 浏览量

146 浏览量

254 浏览量

104 浏览量

177 浏览量

2013-03-15 上传

182 浏览量

167 浏览量

点击了解资源详情

weixin_38696196

- 粉丝: 9

最新资源

- dubbo-admin-2.5.8完美整合JDK1.8无错运行指南

- JSP+SSH框架小区物业管理系统设计与实现

- 桌面宠物与桌面锁功能的VC源码教程

- Java字符过滤机制:BadInputFilter实践解析

- RegAnalyzer:数字逻辑开发中用于bit级寄存器分析工具

- 交互式数据探索:掌握ipython, vim, slimeux提高计算效率

- Matlab中使用CNN处理MNIST数据集

- 新版免疫墙技术突破,系统安全防护升级

- 深入探索Qt库中的对象关系映射技术

- QT递归算法在Windows下绘制二叉树

- 王兆安主编《电力电子技术》第五版课件介绍

- Rails Footnotes:提升Rails应用调试效率的信息展示工具

- 仿通讯录地址选择控件的设计与实现

- LED时间字体设计与电子手表字体对比

- Diglin_Chat: 快速集成Zopim聊天服务到Magento平台

- 如何通过QQ远程控制关闭计算机