Nios II双核系统构建与通信实践

"该文档详述了如何进行Nios II双核开发,提供了一个简单的功能实现案例,涉及FPGA和Nios II处理器的硬件连接、地址设置以及软件部分的构建和调试方法。"

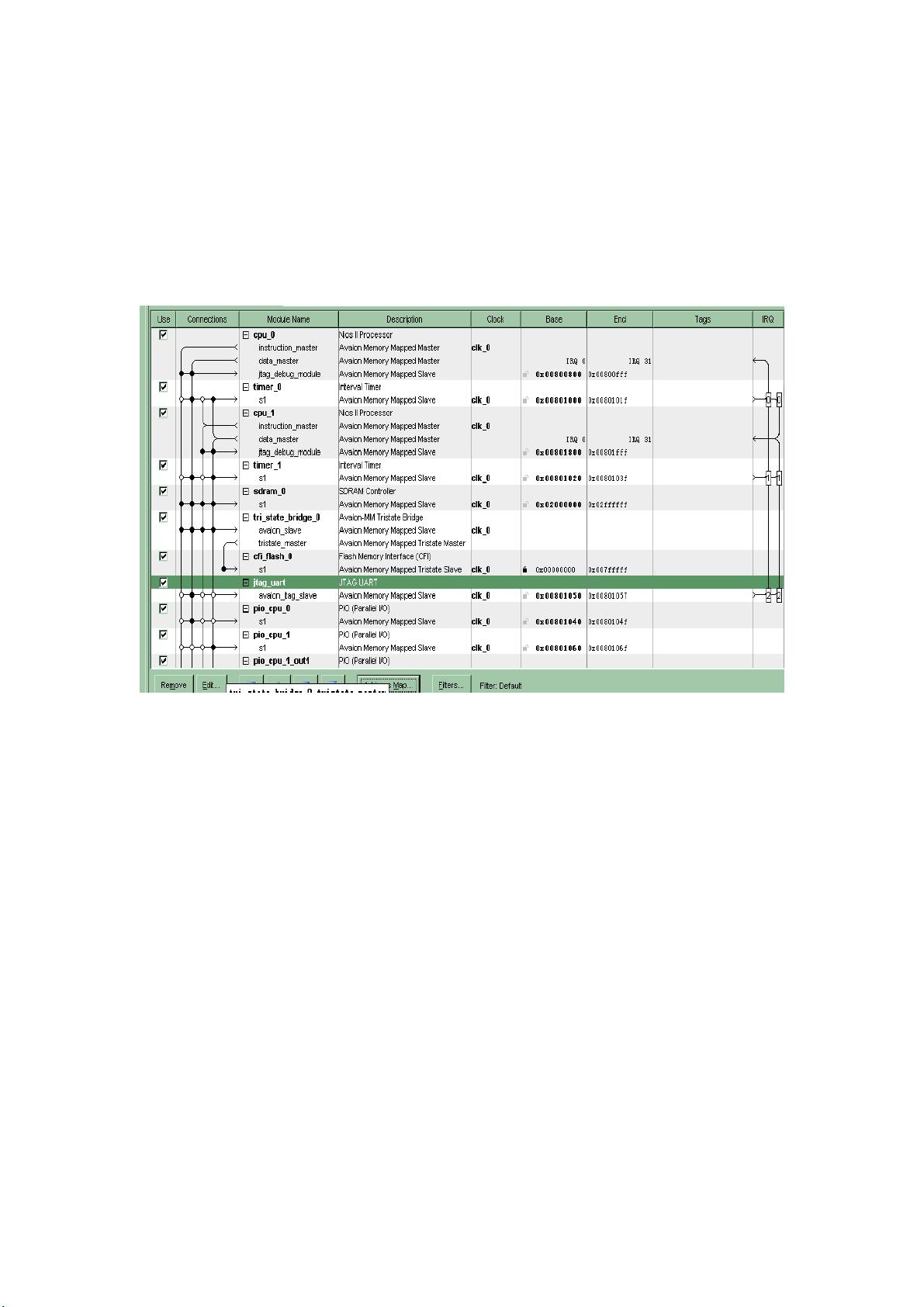

在Nios II双核开发中,工程师需要理解如何构建和管理两个处理器之间的通信。本示例中,Cpu_0控制一个PIO(Peripheral Input/Output)端口,使其输出高电平。这个高电平信号被Cpu_1的PIO接收,当检测到高电平时,Cpu_1会使得自身的PIO输出pio_cpu_1_out1每隔0.5秒翻转一次,以驱动LED灯变化,从而展示双核间的通信。

硬件连接方面,文档指出两个CPU各有一个定时器,并且都与SDRAM连接,共享指令和数据线。此外,CFI_FLASH_0(并行Flash)通过三态桥与两个CPU交互,JTAG_UART用于调试,而PIO则作为双核间通信的简单手段。值得注意的是,硬件配置文件(sof文件)通常不直接烧录到并行Flash中,而是通过EPCS控制器在Quartus II中预先烧录到EPCS存储器中,确保配置数据在掉电后不会丢失。

在地址设置上,每个CPU的复位地址和异常地址至关重要。Cpu_0的起始偏移地址为0x0,而Cpu_1的起始地址为0x100000,这意味着为Cpu_0分配了1MB的代码空间,而Cpu_1的代码空间则在1MB之后。根据实际的Flash容量,这个地址分配可以调整。

在软件部分,双核开发需要为每个CPU创建单独的工程。调试时,可以使用JTAG接口实现两个工程的联合调试,首先需通过JTAG将sof文件下载到FPGA。在软件烧写环节,要确保重新上电后程序能从Flash正确加载到SDRAM中,并继续运行。

Nios II双核开发涉及到硬件设计、地址映射、软件构建和调试等多个层面,通过合理的配置和设计,可以实现高效的多核系统协同工作。

206 浏览量

2024-11-06 上传

2024-11-06 上传

253 浏览量

269 浏览量

131 浏览量

181 浏览量

qiuxiaohui1234

- 粉丝: 5

最新资源

- Linux游戏编程入门

- WebWork教程0.90版:初稿发布

- 掌握微软C编程精华:打造无错程序秘籍

- GCC:Linux系统的高效多平台编译器

- GNUgcj:Free Software Foundation的编程工具

- 图形博士GraPhD®软件使用手册(二)

- Java RMI:构建分布式应用

- 《Linux内核完全注释》赵炯著 - 内核版本0.11详解

- 2006年程序员资格考试试题解析

- 自定义SoDA模板:设计模型与UseCase实例

- 计算机病毒演变与反制策略探讨

- Java连接SQL Server数据库实战经验分享

- C#完全指南:从入门到精通

- 数据结构实战:冒泡排序与斐波那契序列算法解析

- Acegi安全框架在Spring Web应用中的实战指南

- Java开发者指南:Eclipse实战