数字化调频收音机:锁相环与单片机应用实现高精度调谐

93 浏览量

更新于2024-09-01

1

收藏 138KB PDF 举报

本文档探讨的是数字式调频收音机的设计,主要集中在利用现代技术改进传统调谐和本振电路的方法。在传统收音机中,调谐和本振电路通常依赖于电容和电感的手动调整,然而,随着无线电通信技术的进步,锁相环(PLL)和频率合成技术的应用日益广泛。PLL因其跟踪特性、窄带滤波能力和锁定状态下的无剩余频差,使得它在频率合成中成为高频准确度极高的信号源的关键。

设计的核心理念是采用PLL作为频率合成器,通过单片机(如MCS-51系列)来精确控制PLL内的分频数,从而实现对输出频率的精细调整,以满足调台的需求。设计的主要要求包括:

1. 接收FM信号的频率范围必须覆盖88-108MHz,这是广播频段的主要部分。

2. 调制信号的频率范围从100Hz到15000Hz,且频偏限制在75kHz,确保信号质量稳定。

3. 设计要求输出不失真功率至少为100mW,针对典型的8欧姆负载。

4. 接收机的灵敏度要达到或低于1毫瓦,以便在较弱信号环境中仍能正常工作。

5. 镜像抑制性能需优于20分贝,以减少干扰信号的影响。

6. 收音机应具备数字化功能,包括自动搜台、手动调台、存储频道和实时显示频率。

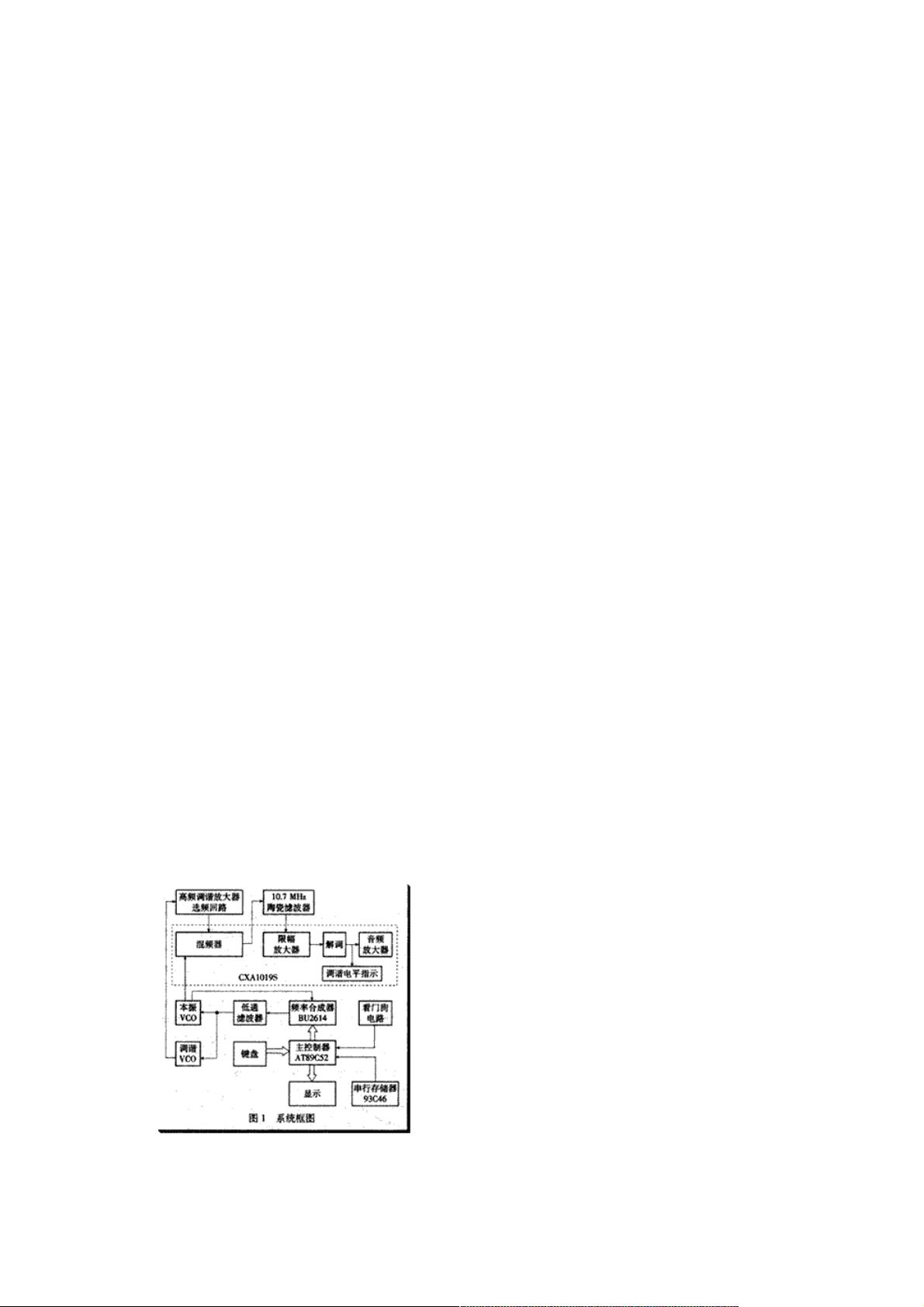

整个系统设计采用了专门的集成芯片,如CXA1019S负责高放、混频、中放和解调等基本功能,而锁相频率合成器BU2614则负责自动调谐和频率控制。MCS-51系列单片机负责控制 PLL 和相关的功能,例如改变分频比,同时通过串行接口与BU2614协作。此外,MAX7219和93C46芯片则用于显示功能,如选台操作和频率显示,以及存台管理。

数字式调频收音机设计不仅提升了传统收音机的精度和便利性,还引入了数字化控制和自动化特性,使得整个系统的性能更加强大和高效。

258 浏览量

193 浏览量

2024-06-26 上传

2012-09-06 上传

2023-06-29 上传

2023-09-03 上传

weixin_38557068

- 粉丝: 4

最新资源

- Verilog实现的Xilinx序列检测器设计教程

- 九度智能SEO优化软件新版发布,提升搜索引擎排名

- EssentialPIM Pro v11.0 便携修改版:全面个人信息管理与同步

- C#源代码的恶作剧外表答题器程序教程

- Weblogic集群配置与优化及常见问题解决方案

- Harvard Dataverse数据的Python Flask API教程

- DNS域名批量解析工具v1.31:功能提升与日志更新

- JavaScript前台表单验证技巧与实例解析

- FLAC二次开发实用论文资料汇总

- JavaScript项目开发实践:Front-Projeto-Final-PS-2019.2解析

- 76云保姆:迅雷云点播免费自动升级体验

- Android SQLite数据库增删改查操作详解

- HTML/CSS/JS基础模板:经典篮球学习项目

- 粒子群算法优化GARVER-6直流配网规划

- Windows版jemalloc内存分配器发布

- 实用强大QQ机器人,你值得拥有