Verilog HDL深度教程:硬件开发新手入门

需积分: 5 48 浏览量

更新于2024-07-23

收藏 1.73MB PDF 举报

"本资源是一份关于Verilog HDL的深度教程,适合硬件开发新手学习。教程详尽地介绍了数字信号处理、计算、程序、算法和硬线逻辑的基础知识,帮助读者理解在现代电子设备中这些技术的应用。"

在电子工程和计算机科学中,Verilog HDL(硬件描述语言)是一种至关重要的工具,它被用来描述数字系统的结构和行为。这个经典教程深入浅出地讲解了Verilog的基础和应用,尤其对于那些刚刚接触硬件设计的人来说是一个很好的起点。

首先,教程中提到了数字信号处理(DSP)的基本概念,这是现代计算机和通信系统的核心组成部分。DSP涉及对数字信号的滤波、变换、加密解密等一系列操作,这些操作通常是基于数学算法的。虽然理论上可以使用通用计算机或微处理器来执行这些算法,但有时为了效率和实时性,我们会选择专门设计的硬件系统,例如 FPGA(现场可编程门阵列)或ASIC(专用集成电路)。

教程通过实例说明了实时和非实时数字信号处理的区别。非实时处理,如在石油地质调查中的数据处理,可以使用通用计算机在较长时间内完成,而不影响结果的准确性。然而,对于像军用通信或雷达系统这样需要快速响应的实时应用,通用处理器的灵活性和速度就显得不足。这时,设计专用的硬线逻辑电路,比如在高速FPGA上实现,成为首选方案。这是因为通用微处理器需要通过指令集进行操作,执行速度受限于时钟周期,而硬线逻辑则是直接由硬件电路实现,速度远超软件执行。

Verilog HDL正是设计这种硬线逻辑电路的语言,它允许工程师以抽象的方式描述硬件的行为,然后通过合成工具转化为实际的电路布局。通过学习这个教程,读者将能够理解和创建自己的Verilog模块,用于实现各种复杂的数字信号处理功能。

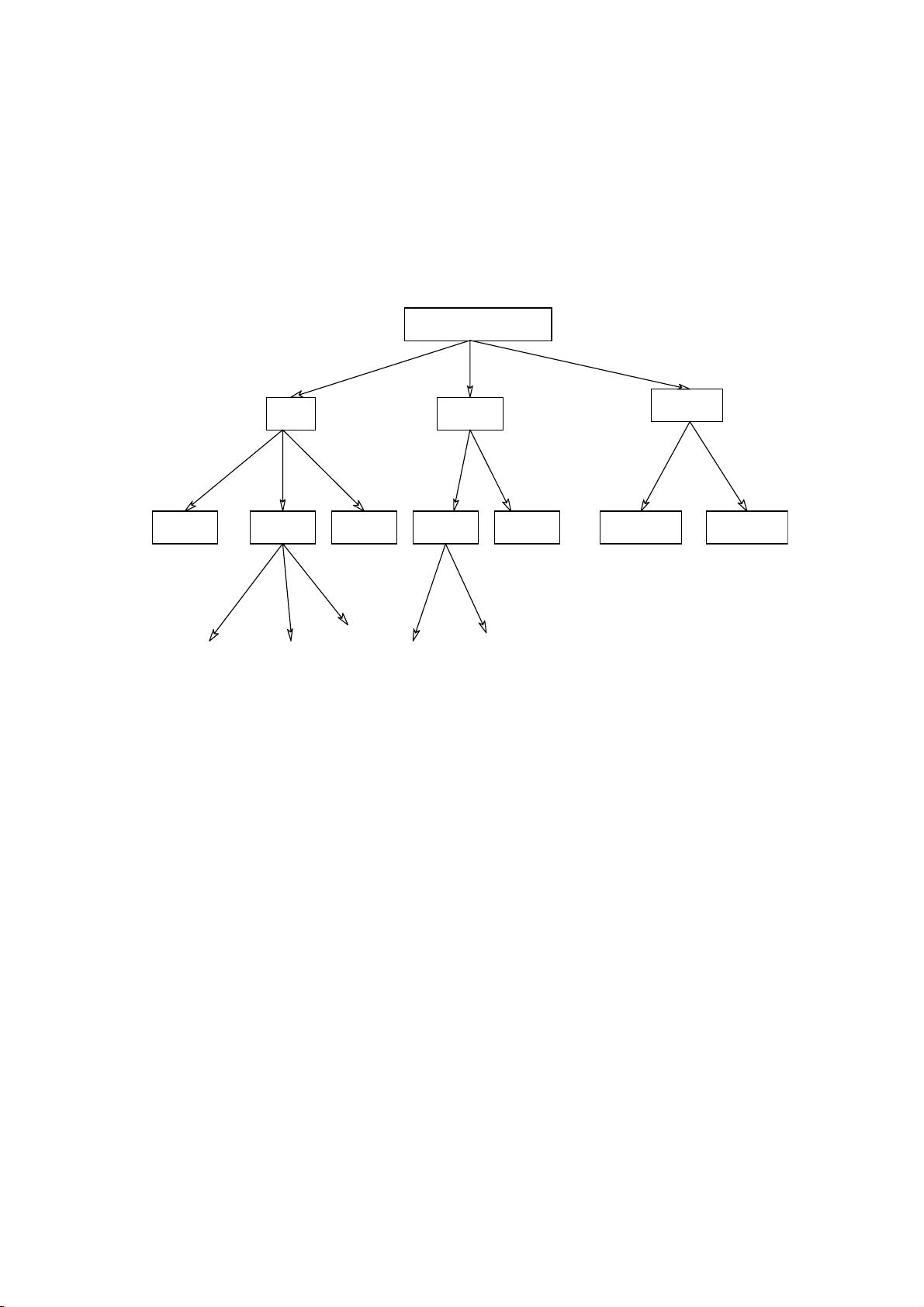

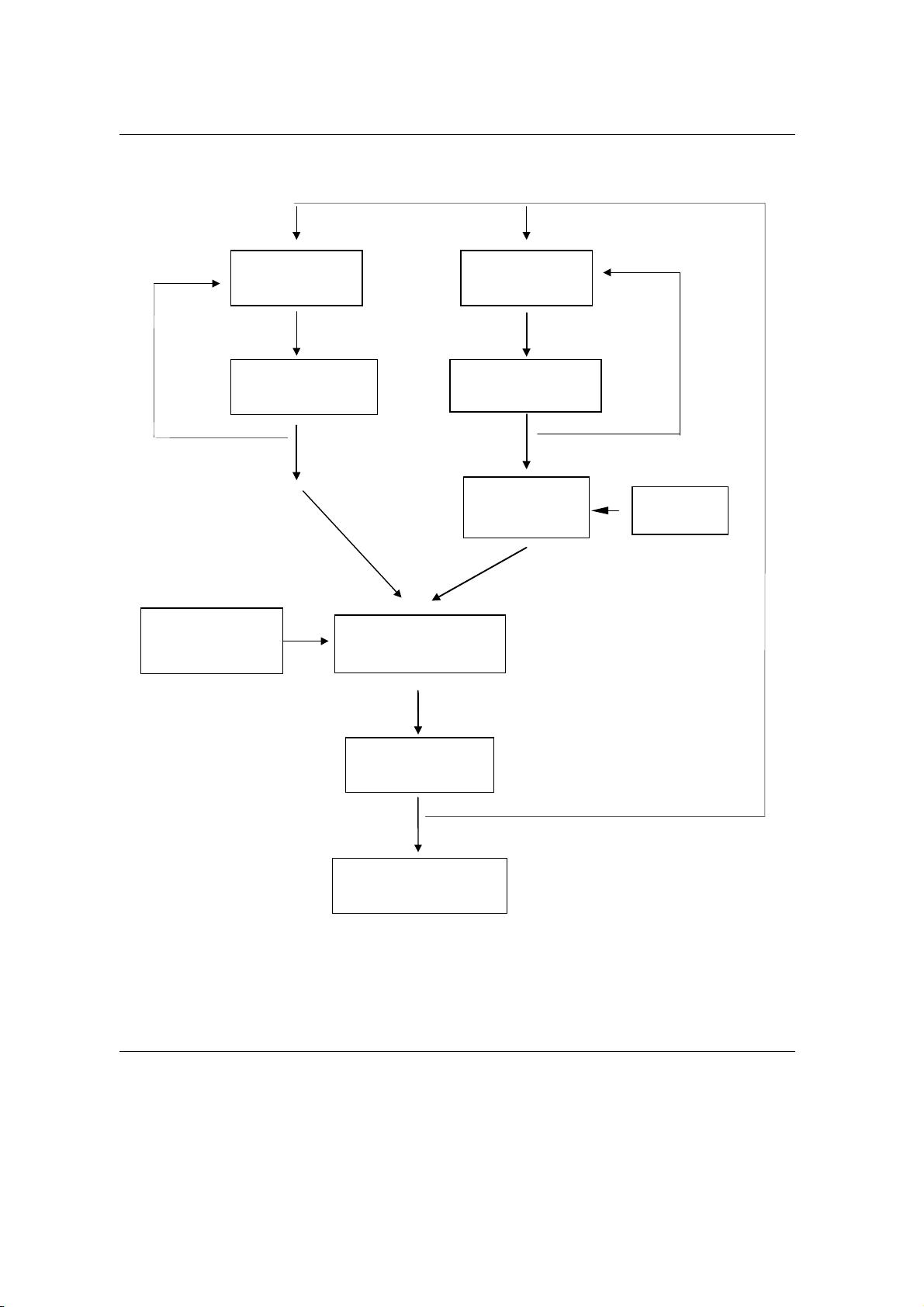

在学习过程中,读者会了解到如何使用Verilog描述算法,如何构建基本逻辑门,如何组织更复杂的逻辑单元,以及如何进行仿真验证,确保设计的功能正确无误。此外,还会接触到FPGA设计流程,包括综合、布局布线以及最终的硬件测试。

这个Verilog经典教程是进入硬件设计领域的良好起点,它不仅涵盖了Verilog的基础语法,还深入探讨了硬件设计在实际应用中的挑战和解决方案,特别是与数字信号处理相关的部分。通过学习,初学者不仅可以掌握Verilog语言,还能理解硬件设计背后的原理,为未来在FPGA或ASIC设计领域的工作打下坚实基础。

2008-09-13 上传

2008-10-30 上传

2011-10-10 上传

2022-07-15 上传

2013-05-29 上传

yanhai116

- 粉丝: 0

- 资源: 2

最新资源

- IEEE 14总线系统Simulink模型开发指南与案例研究

- STLinkV2.J16.S4固件更新与应用指南

- Java并发处理的实用示例分析

- Linux下简化部署与日志查看的Shell脚本工具

- Maven增量编译技术详解及应用示例

- MyEclipse 2021.5.24a最新版本发布

- Indore探索前端代码库使用指南与开发环境搭建

- 电子技术基础数字部分PPT课件第六版康华光

- MySQL 8.0.25版本可视化安装包详细介绍

- 易语言实现主流搜索引擎快速集成

- 使用asyncio-sse包装器实现服务器事件推送简易指南

- Java高级开发工程师面试要点总结

- R语言项目ClearningData-Proj1的数据处理

- VFP成本费用计算系统源码及论文全面解析

- Qt5与C++打造书籍管理系统教程

- React 应用入门:开发、测试及生产部署教程