基于VHDL的FPGA实现51单片机IP核设计

需积分: 50 71 浏览量

更新于2024-07-09

2

收藏 307KB PDF 举报

"基于FPGA的完全兼容51单片机的IP核设计,通过VHDL语言实现,包括MCS-51内核解析、系统规划、译码控制模块设计与实现。"

本文主要探讨了如何使用FPGA(Field-Programmable Gate Array)技术设计一个完全兼容8051内核的IP( Intellectual Property)核。8051单片机,也称为MCS-51,是集成电路领域中的经典产品,自1980年以来因其强大的功能和易用性而广泛应用于各种嵌入式系统。随着技术的发展,FPGA成为实现复杂数字逻辑电路的新选择,使得设计者能够利用硬件描述语言(如VHDL)来创建自定义的集成电路。

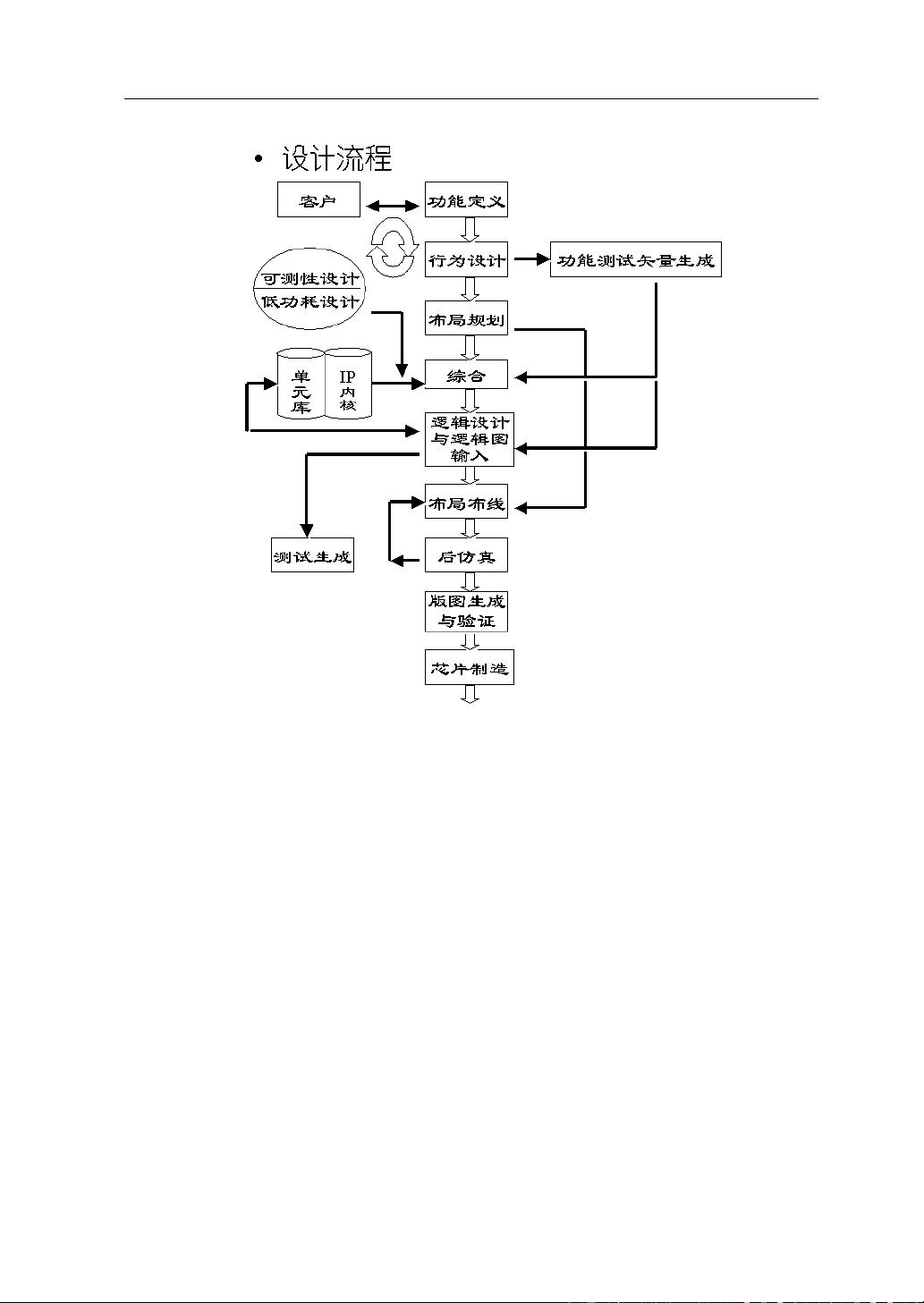

首先,文章介绍了集成电路设计的基础知识,包括集成电路的发展历程、设计流程和设计方法。集成电路设计流程涵盖了从概念设计到最终产品的全过程,包括需求分析、系统设计、逻辑设计、布局布线和验证。在设计方法中,VHDL作为一种硬件描述语言,被广泛用于描述数字系统的功能和行为。

VHDL是IEEE标准定义的一种高级语言,它允许设计者以结构化的方式描述硬件系统,同时支持行为和结构化描述。在本论文中,VHDL被用来实现MCS-51单片机的各个功能模块,包括指令系统、时序控制和接口控制等。

MCS-51单片机的总体结构被详细剖析,包括其硬件结构特点、引脚描述和内部结构。该单片机的指令系统是其核心部分,论文深入解析了CPU时序和指令分解,这为后续的IP核设计提供了基础。

在系统设计阶段,作者将MCS-51的指令集和功能分解为多个模块,并对这些模块进行了初步划分,如算术逻辑单元(ALU)、存储器控制、输入/输出(I/O)管理等。每个模块的功能和接口设计都进行了说明,以便于在FPGA上实现。

重点章节集中在译码/控制模块的设计和实现。这一模块是单片机的心脏,负责解码指令并生成控制信号以协调整个系统的工作。作者详细阐述了设计思想和实现过程,包括接口信号和控制信号的生成,这是确保IP核正确执行8051指令的关键。

最后,论文总结了设计过程中取得的阶段性成果和经验心得,同时也指出了存在的不足和未来可能的改进方向。通过这种方式,为FPGA上的MCS-51单片机实现提供了一套完整的参考方案,对于理解FPGA设计和8051单片机原理有重要的实践价值。

2024-06-24 上传

2024-03-13 上传

120 浏览量

2024-03-16 上传

223 浏览量

165 浏览量

weixin_38688550

- 粉丝: 7

- 资源: 912

最新资源

- apiAutocomNFSe

- ekrtf304_d7_delphi_rtf_3娱d7com_

- mysql-installer-community-8.0.22.0.msi.zip

- blomqvist:布隆奎斯特

- zsnap:Linux上用于ZFS的自动简单快照工具

- 记分卡:安全记分卡-开源的安全健康指标

- 用HTML5编写乐谱

- java项目实战练习小项目

- typed-manifest:对标准 Java META-INFMANIFEST.MF 的类型安全访问

- firefox-to-deepl:Firefox扩展。 突出显示网页上的文本并将其发送到DeepL

- 关于车辆到行人通信系统及其使用方法的介绍说明.rar

- 基于串口通信的上位机控制软件.rar

- Week5:网络编程

- t-angular-boilerplate-keycloak

- svelte-localstorage::warning:尚未就绪:warning:自动与localStorage同步的Svelte可写存储

- matlab个人练习上手视觉项目