FPGA时序优化策略与步骤详解

需积分: 49 108 浏览量

更新于2024-07-18

2

收藏 2.43MB PDF 举报

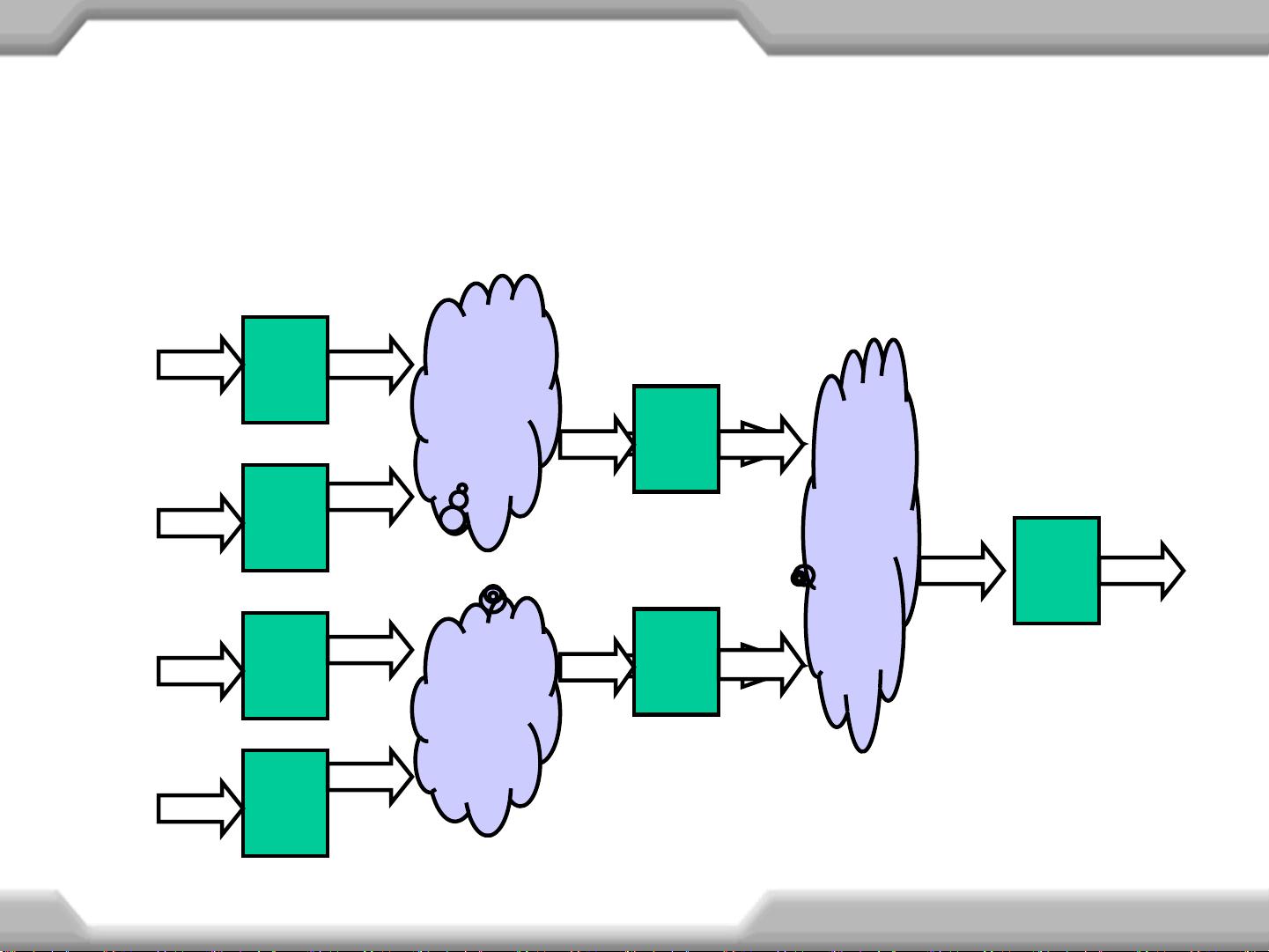

FPGA时序优化方法是一门关键的技能,特别是在设计复杂集成电路时,确保电路能够在预定的时间内正确运行至关重要。本文档详细阐述了如何有效地解决FPGA设计中的时序问题,并通过一系列步骤实现时序收敛。

首先,课程内容涵盖了时序收敛的基本流程,这是设计过程中不可或缺的部分。时序收敛涉及到前端综合与后端布局布线的反复迭代,目标是通过调整设计参数、优化技术和修改布线结构来减小延迟,直至所有路径的时序满足预设要求。在这个过程中,设计者会利用项目导航器(ProjectNavigator)生成Post-Map和Post-Place&Route的静态时序报告,这些报告提供了详细的路径信息,帮助分析未满足时序的原因。

其次,设计的成功评判标准包括:面积利用率不超过85%,以确保设计可以在选定的FPGA器件上实施;工作频率必须达到或超过性能需求;以及管脚定义的准确性,如信号名称、位置、电平标准和数据流方向等。此外,评估设计是否适合特定芯片,需考虑芯片的资源容量,如逻辑单元的数量,以及内存资源的比特位数。通过查看MapReport和Place&RouteReport,可以判断设计是否能完全布通且不会超出芯片的承载能力。

在优化过程中,性能突破的关键在于合理利用内置IP资源,如DSP48、PowerPC处理器、EMAC、SDR/DDR控制器、FIFO和blockRAM等,同时采用同步设计方法,确保代码针对关键路径进行了优化。此外,使用高级综合工具和布局布线工具时,应尝试不同的优化技术,如添加精确的时序约束,以便在synthesis阶段就考虑到时序性能。

总结来说,FPGA时序优化是一个系统性的工程,需要结合工具和技术,从设计初期到后期迭代,不断调整以达到最佳的时序性能。掌握这个流程对于实现高性能和高效率的FPGA设计至关重要。通过深入理解时序收敛、资源利用和性能优化策略,设计师能够提升项目的成功率并减少设计周期。

1417 浏览量

350 浏览量

212 浏览量

518 浏览量

115 浏览量

185 浏览量

stayoyo

- 粉丝: 8

- 资源: 8

最新资源

- uexam学之思在线考试系统 v3.0.7

- MT48LC32M16A2TG-75_IT_SDRAM_it_BGA_

- koaVote:使用Koa的非常简单的投票网站

- SubDomainizer:一种工具,用于查找子域和隐藏在其中的有趣内容,页面,文件夹和Github的外部Javascript文件

- php_demon_laravel_admin:通用PHP-ADMIN-LARAVEL快速开发库

- 在OpenGL中生成轮廓

- nodemvc:另一个节点 mvc

- app5

- artsy-timelines:一个简单的Web应用程序,用于在交互式时间轴上(通过Artsy API)呈现艺术品,艺术家,“基因”和标签

- 基于fpga的示波器(quartus13.0).zip

- 灵丹妙药:分享您生动故事的安全空间

- reinforcement_learning_agents:RL代理商库

- sim_test_

- s_task:C的等待协程库

- clas12-mcgen:所有CLAS12 MC事件生成器的集合

- Tinyxml库和学习文档以及上手即可运行的实例