PCIe体系结构解析:从PCI到PCI Express的发展

下载需积分: 10 | PDF格式 | 3.78MB |

更新于2024-07-16

| 99 浏览量 | 举报

“经典之作_浅谈PCI_Express体系结构.pdf”是一份关于PCI和PCI Express技术的详细教程,内容涵盖PCI Express体系结构的基础知识和历史背景。

本文将深入探讨PCI Express(PCIe)体系结构,它是现代计算机系统中广泛使用的高速接口标准。PCIe是由PCI发展而来,旨在提供比传统PCI更高的数据传输速率和更低的延迟,以适应不断增长的处理器性能需求。

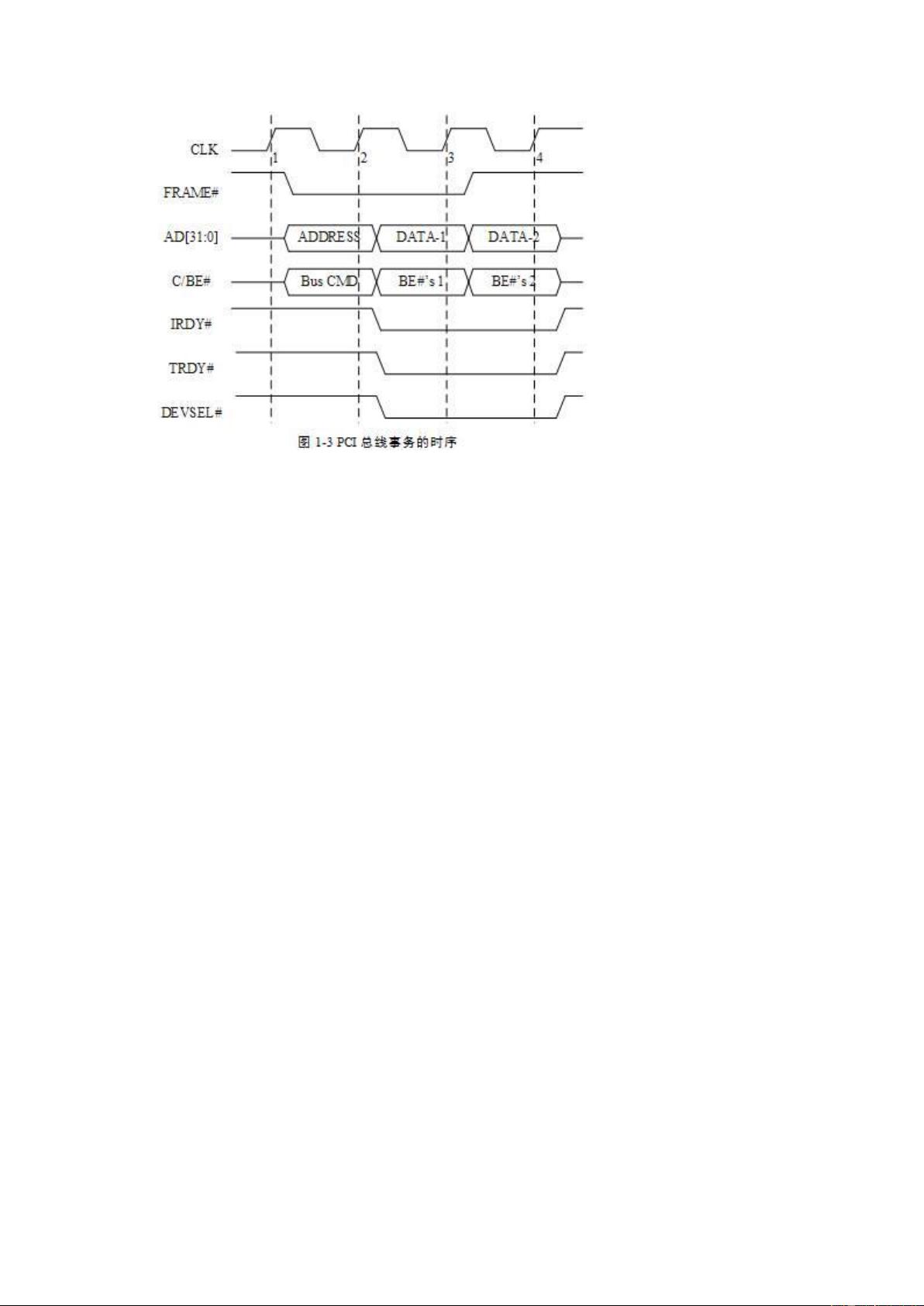

首先,PCI(Peripheral Component Interconnect)总线自1990年代初推出以来,就成为了个人计算机(PC)内部扩展设备连接的标准。它作为一种局部总线,是系统总线的扩展,用于连接诸如显卡、声卡等外部设备。随着处理器速度的提升,对总线速度和带宽的需求也相应增加。PCI总线的出现迅速替代了ISA、EISA、VESA和MCA等旧有的总线标准,因为它提供了更高的性能和更好的兼容性。

PCI总线规范经历了多个版本的演进,从最初的16位、32位,再到64位,带宽逐渐增大。然而,随着时间推移,PCIe(PCI Express)作为其下一代标准,应运而生。PCIe采用了串行传输方式,与传统的并行PCI总线相比,能提供更高的数据传输速率,同时降低了信号干扰问题。PCIe接口采用点对点连接,每个设备都有独立的通道,从而实现更高的带宽利用率。

在软件层面,PCIe与PCI保持兼容,这意味着系统可以继续使用现有的PCI驱动程序来管理PCIe设备。而在硬件层面,尽管PCIe在设计上做了很多改进,如采用更复杂的交换结构和更高效的错误处理机制,但它依然保留了PCI的一些核心设计理念,如配置空间和中断处理机制,使得迁移成本降低,系统设计更为简便。

PCI总线V1.0规范最初只适用于单个PCB(Printed Circuit Board)上的设备连接,但随着技术的发展,PCIe已经发展出多种速度等级(例如PCIe x1、x2、x4、x8、x16等),支持多路复用,满足了从低速I/O设备到高性能显卡和网络适配器等多种设备的需求。

了解PCI和PCIe总线对于硬件和软件工程师来说至关重要,因为它们构成了现代计算机系统中的关键部分。无论是设计新的系统,还是优化现有设备的性能,都需要对这些接口标准有深入的理解。通过这份资料,读者可以全面掌握PCI和PCIe的历史、工作原理以及它们在当前计算机架构中的作用。

相关推荐

2294 浏览量

勤奋的小石子

- 粉丝: 17

最新资源

- PSCP实验室的C++编程实践探索

- 137套BusinessSkinForm皮肤及控件的安装与使用指南

- 探索数学建模与实验:第六讲非线性规划深度解析

- 深入解析Android图片加载库Universal Image Loader

- VC++实现的高效进程调度课程设计

- KCCSS:安全评估Kubernetes配置的专家级框架

- ET2012快捷键增强版:CAD软件开发利器

- 掌握ADO.NET数据操作技巧

- 深入解析HTTPS协议及其在Tomcat中的配置方法

- IIS安装包大全:一次性下载安装无忧

- PHP事务处理与防SQL注入实践Demo

- Windows 64位Redis官网下载及安装教程

- 快速搭建本地物流信息发布平台教程

- 监控录像转换工具:svcSetup.exe使用指南

- Standard ML编程语言的核心特性与应用

- 深入线性规划与MATLAB应用课程学习