FPGA校招笔试精华:同步FIFO深度计算与抗混滤波应用

本资源是一份针对FPGA校招面试的笔试经验总结,主要涵盖了以下几个知识点:

1. **同步FIFO深度计算**:同步FIFO的设计中,关键在于理解写入和读取的数据速率比。题目给出的例子中,每100个写时钟周期可以写入80个数据,每10个读时钟周期可以读出8个数据。当写时钟频率(w_clk)等于读时钟频率(r_clk)时,可以通过以下公式计算FIFO的最小深度:

```

fifo_depth = burst_length - (burst_length * X / Y) * r_clk / w_clk

```

在提供的例子中,第一个例子中深度为32,第二个例子中深度为48。

2. **2选1 MUX用于异或逻辑**:关于MUX的数量,开始时认为需要3个,但实际上是错误的。实际上,只需要两个2选1 MUX通过级联实现异或逻辑,因为每个MUX可以处理两种输入的一种,组合起来就能完成异或操作。

3. **抗混滤波**:在模拟信号数字化(采样)过程中,抗混滤波器的作用是去除由于采样不足可能导致的频率混叠现象。根据奈奎斯特采样定律,采样频率应至少是信号最高频率的两倍。实际应用中,通常在采样前采用低通滤波器,截止频率fc确定为采样频率的一半减去一小部分余量,如fc = fz / 2.56。

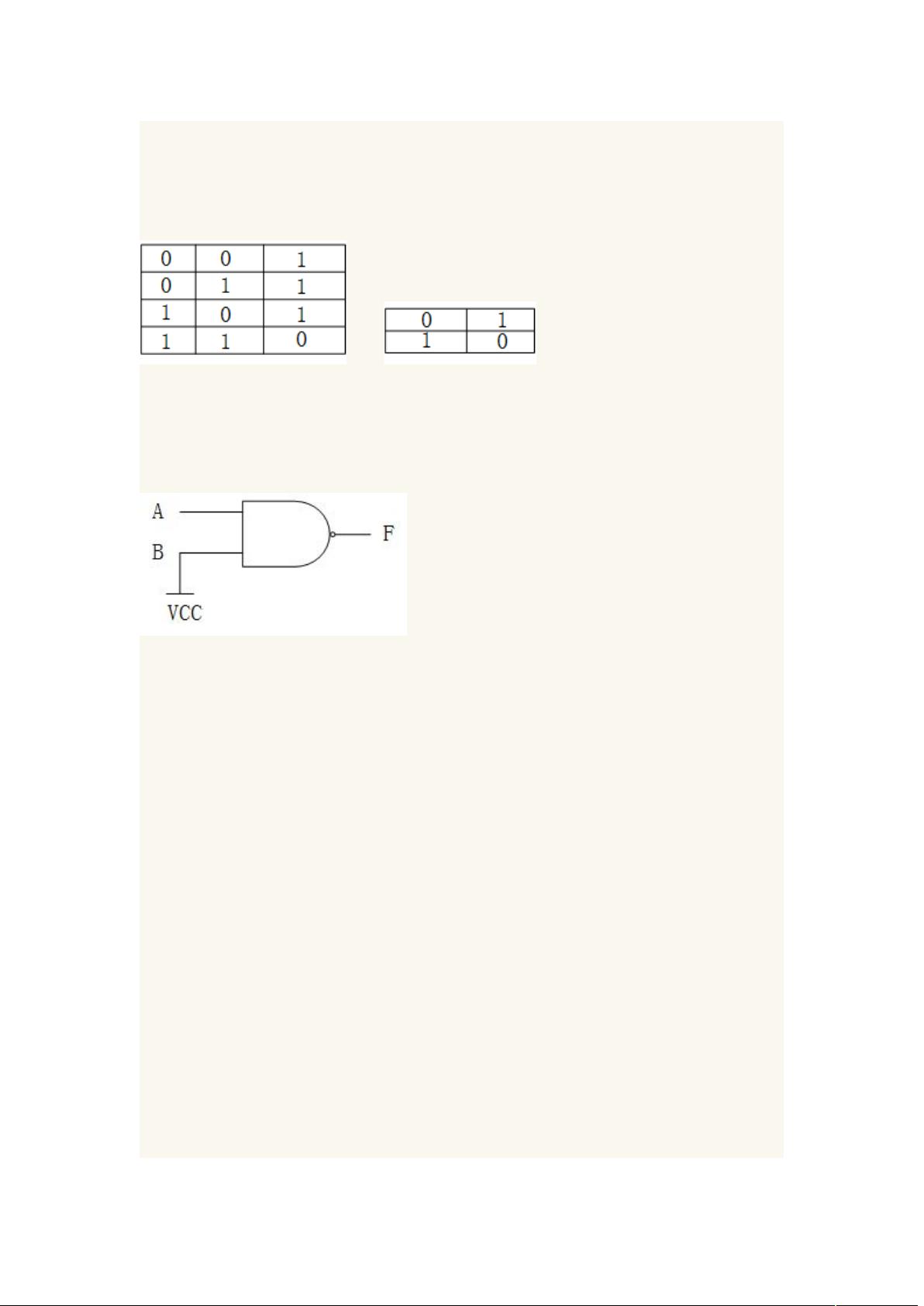

4. **线与逻辑与上拉电阻**:线与逻辑是通过两个输出信号并联实现“与”功能,可以利用OC或OD门,为了保证逻辑稳定,需要在输出端添加一个上拉电阻,防止输出悬空。

5. **与非门的非门使用**:将二输入与非门当作非门使用时,由于与非门具有“有0出0,全1出1”的特性,当将其一端接至逻辑0时,相当于实现了非门的功能。因此,将与非门的非门输入端接到高电平,即可将其视为非门使用。

这份总结提供了FPGA面试中常见的问题及解答,对于准备FPGA方向校招的同学来说,这些内容有助于理解和掌握基本概念,并提升考试应对能力。

点击了解资源详情

点击了解资源详情

423 浏览量

263 浏览量

1604 浏览量

203 浏览量

6000 浏览量

yu1037764299

- 粉丝: 154

最新资源

- 革新操作体验:无需最小化按钮的窗口快速最小化工具

- VFP9编程实现EXCEL操作辅助软件的使用指南

- Apache CXF 2.2.9版本特性及资源下载指南

- Android黄金矿工游戏核心逻辑揭秘

- SQLyog企业版激活方法及文件结构解析

- PHP Flash投票系统源码及学习项目资源v1.2

- lhgDialog-4.2.0:轻量级且美观的弹窗组件,多皮肤支持

- ReactiveMaps:React组件库实现地图实时更新功能

- U盘硬件设计全方位学习资料

- Codice:一站式在线笔记与任务管理解决方案

- MyBatis自动生成POJO和Mapper工具类的介绍与应用

- 学生选课系统设计模版与概要设计指南

- radiusmanager 3.9.0 中文包发布

- 7LOG v1.0 正式版:多元技术项目源码包

- Newtonsoft.Json.dll 6.0版本:序列化与反序列化新突破

- Android实现SQLite数据库高效分页加载技巧