高速PCB设计技术详解:布局、布线与仿真

需积分: 15 32 浏览量

更新于2024-07-31

收藏 1.14MB PDF 举报

“高速PCB设计和布线设计涉及抑制EMI干扰,关注高速PCB设计流程、叠层设计、走线阻抗、电源分配、布局布线原则及测试仿真。”

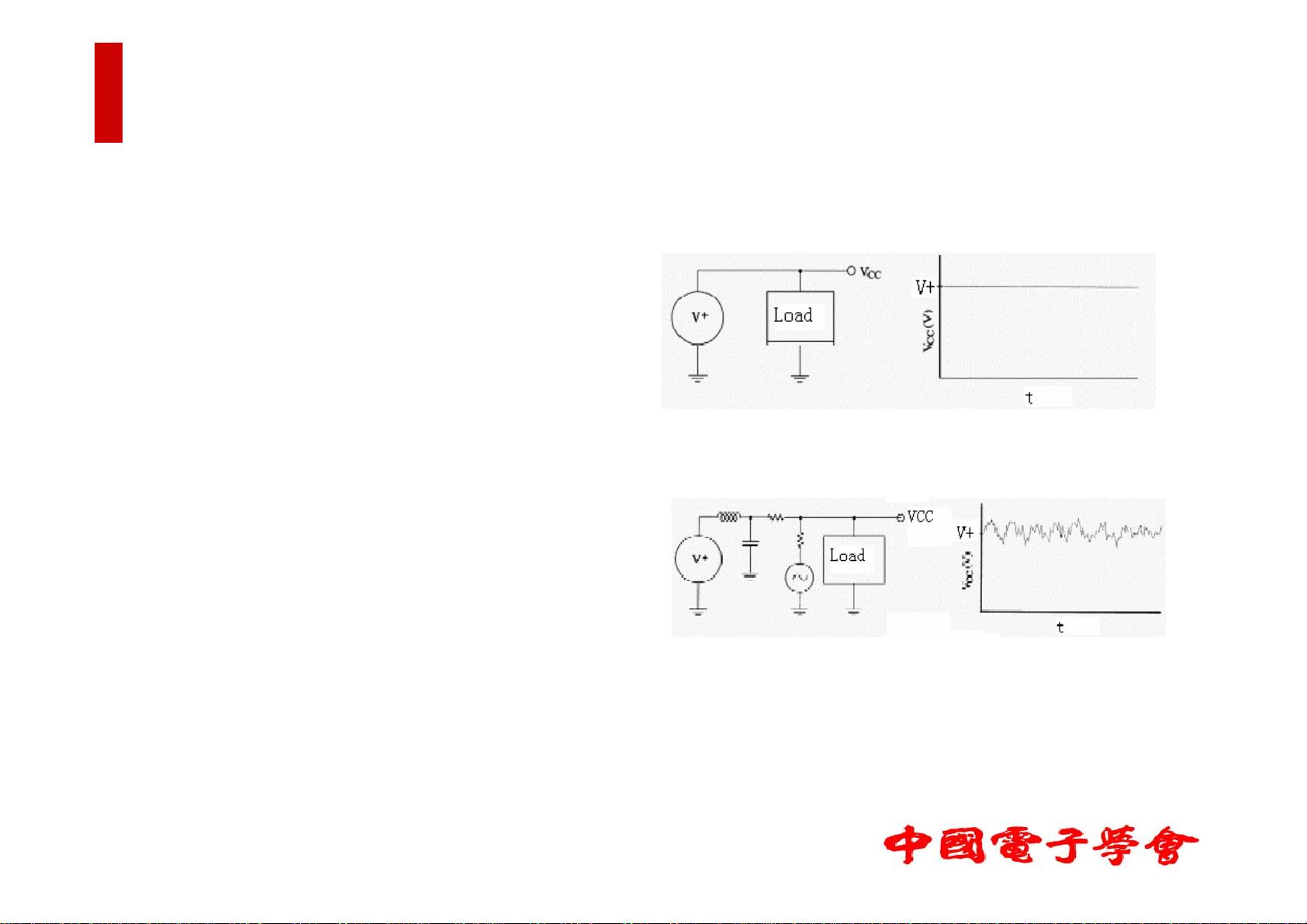

在高速PCB设计中,首要任务是理解整个设计流程。这通常包括预布局和前仿真,布局,布线,以及后仿真。预布局阶段是基于网表和信号特征进行初步布局规划,输出预布局图和规则驱动表。前仿真则用于分析设计的信号完整性(SI)问题。布局阶段侧重于合理安排元件位置,以优化信号传输和减少电磁干扰(EMI)。布线阶段需确保走线符合阻抗控制要求,同时避免串扰。后仿真则是对布线后的电路进行SI测试,确保设计符合预期性能。

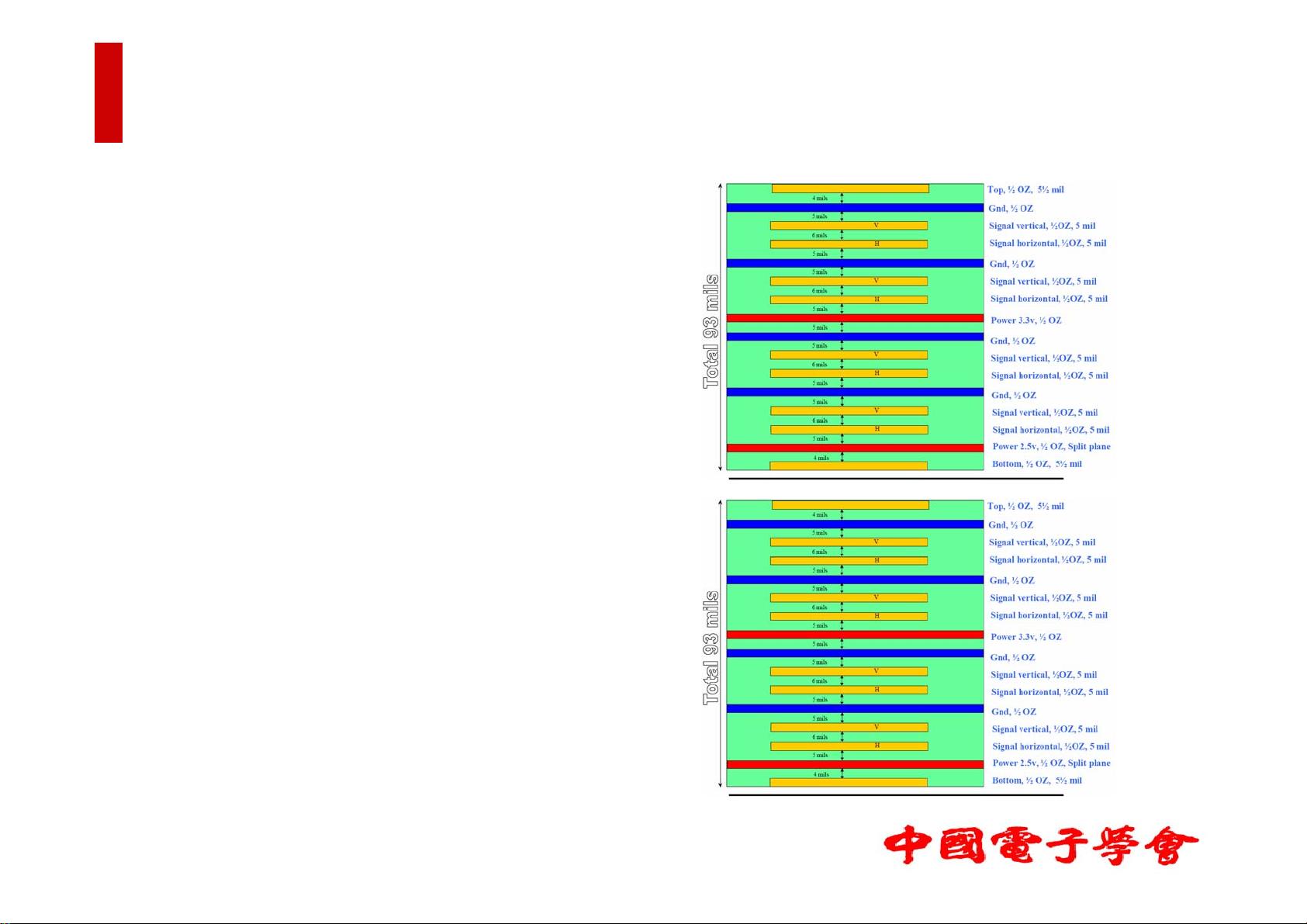

叠层设计是高速PCB设计的关键,因为它直接影响到系统的性能、稳定性和成本。设计时需遵循对称原则,保持电源和地层相邻,地层数量大于等于电源层数,并避免走线层直接相邻。此外,选择合适的板材和确定各层走线厚度也至关重要。例如,一个八层板可能需要两个地层和两个电源层,其余作为信号层,不同叠层配置会有各自的优缺点。

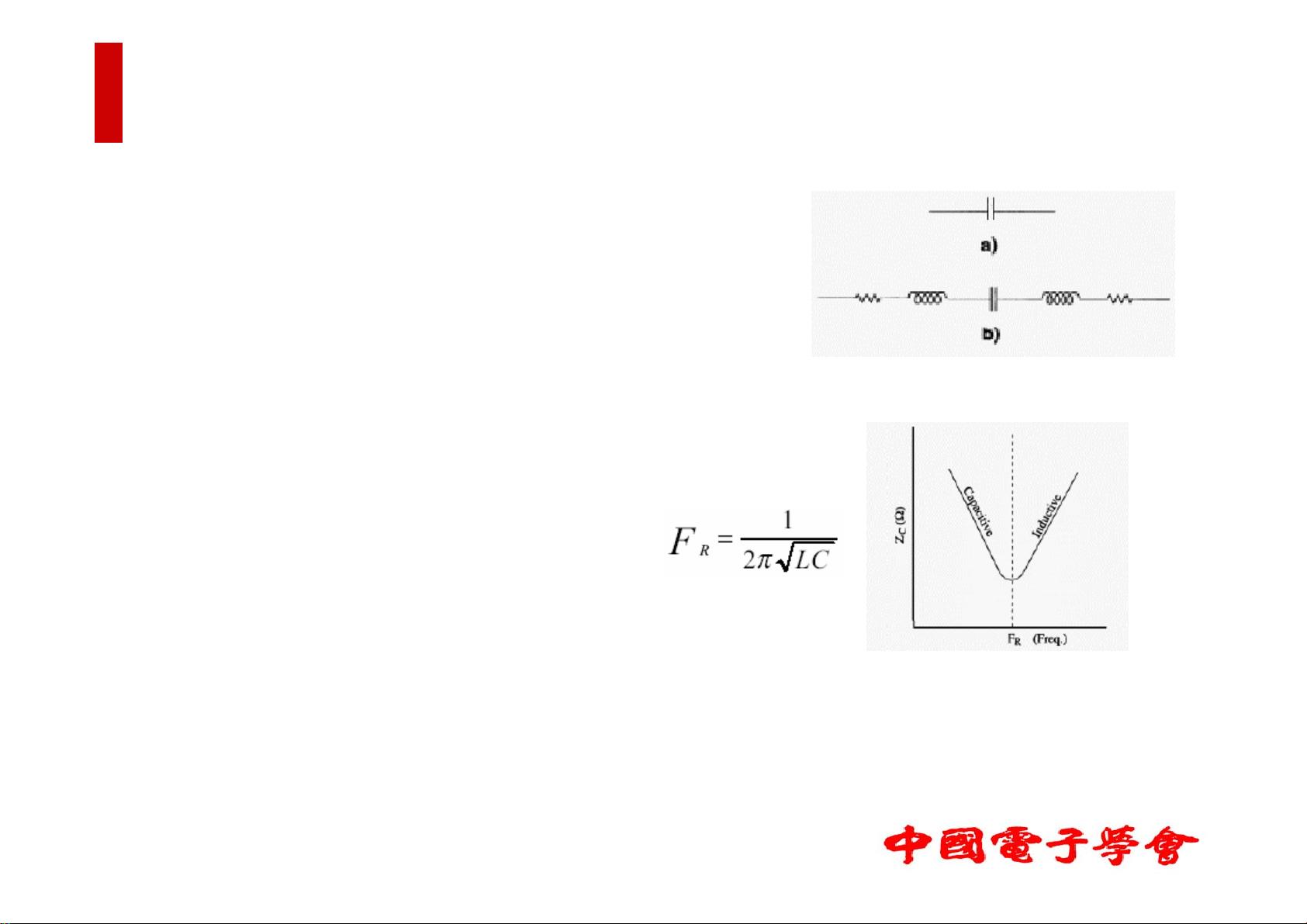

走线阻抗的设计是保证信号完整性的核心。常见的走线阻抗有单端50欧姆和差分100欧姆,但现代设计可能需要更多种类的阻抗,如27欧姆、33欧姆、75欧姆和120欧姆。为了实现这些阻抗,需要精确控制走线宽度。单线阻抗50欧姆的设计要求误差控制在±10%以内,而差分阻抗100欧姆的设计同样需要精准的布线策略。

高速PCB设计的布局原则包括最小化信号路径长度,降低环路面积以减少辐射,以及确保敏感信号远离噪声源。布线原则则涉及避免过长的过孔,保持信号线的等长,以及使用适当的线宽和间距以控制阻抗和减小串扰。

仿真在高速PCB设计中扮演着不可或缺的角色,它能够预测并解决潜在的信号完整性、电源完整性及EMI问题。常用的PCB设计软件如Altium Designer、Cadence Allegro、 Mentor Graphics的PADS等,各有其优势和适用场景,选择时需根据项目需求和团队熟练度来决定。

高速PCB设计是一门综合了电磁理论、信号完整性、电源完整性及工程实践的复杂学科。良好的高速PCB设计不仅需要深入理解这些原理,还需要熟练掌握相关工具,通过预布局、布局、布线和仿真等步骤,最终实现高效、低干扰的电路板设计。

292 浏览量

511 浏览量

点击了解资源详情

103 浏览量

275 浏览量

125 浏览量

2021-07-25 上传

点击了解资源详情

点击了解资源详情

caomei1208

- 粉丝: 0

- 资源: 2

最新资源

- Lista_de_Exercicios:Lista deExercíciode Algoritmos do Gustavo Guanabara教授

- rust-cas:通过构建与Bazel兼容的内容可寻址商店来测试Rust

- 网络刀客 v3.0

- TW-Shiraz:Shiraz是Tiddlywiki 5的一个小型插件,包含宏,样式表,模板,片段,图像,静态表,动态表,并充当入门工具包

- vc_static_button.rar_RFW_VC static Button_VC++ static Button

- 行业文档-设计装置-一种折叠式太阳能座椅广告棚.zip

- pid控制器代码matlab-Ziegler-Nichols-Tuning-Method:使用Ziegler-Nichols闭环方法针对给定传

- CompletableFuture.zip

- 纯css制作文字随时间变动而变色,文字变色效果,背景透明阴影

- up4

- Curriculum_Vitae:职务経歴书

- 粒子群多目标-程序.rar_UY9_pareto_pareto多目标_多目标 粒子群_自适应粒子群

- 行业文档-设计装置-一种折纸机的机头.zip

- englishTeachers:使用Postgresql的简单应用

- SSM实验室预约管理系统.7z

- ESP8266-01GPIO口模拟I2C LCD1602.rar