60-GHz无线个域网中吉比特RS-CC级联译码器实现

21 浏览量

更新于2024-09-03

收藏 478KB PDF 举报

"本文提出了一种针对60-GHz无线个域网的吉比特里所码(RS)和卷积码(CC)级联译码器设计,采用Viterbi算法的8路并行卷积译码与RiBM算法的里所码译码结构,实现高速、低能耗的编码解码过程。在TSMC 0.13 μm CMOS工艺下,该译码器具有0.135 nJ/bit的能效和5.19 mm2的面积效率,最高吞吐率达到2 Gb/s。"

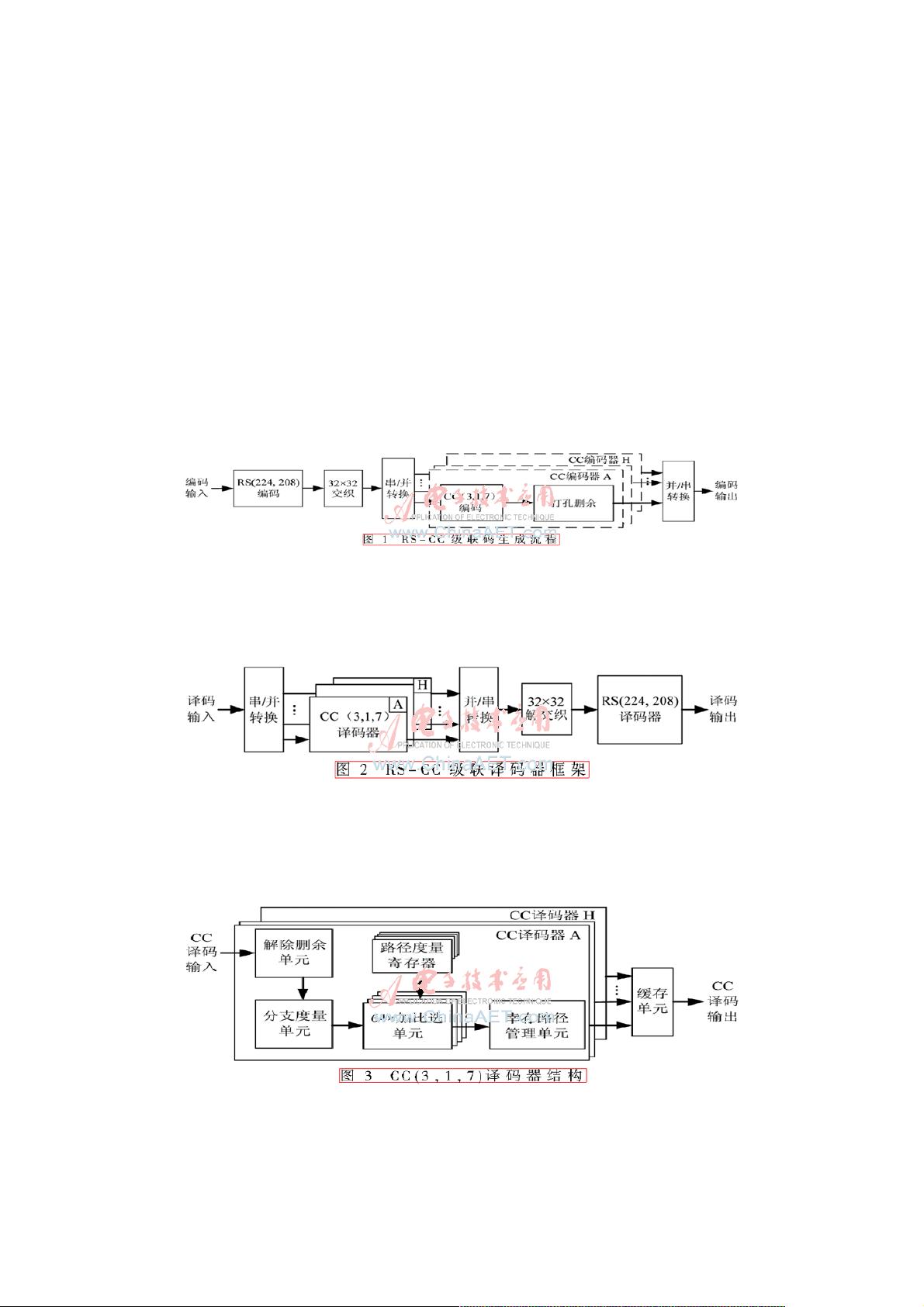

在无线通信领域,尤其是在60-GHz频段的无线个域网中,数据传输速度的需求日益增长。由于高频段的特性,射频非理想因素对系统性能有显著影响。为了解决这些问题,级联编码技术被广泛研究,其中里所码和卷积码的级联使用可以提供更好的错误纠正能力。本文提出的吉比特RS-CC级联译码器正是基于这种思想,利用里所码作为外码,卷积码作为内码,通过交织器连接,形成一种增强的编码方案。

里所码(Reed-Solomon codes)是一种非线性的纠错码,它基于伽罗华域上的多项式运算。在本文中,采用的是RS(255, 239)截断码作为外码,每个编码块包含208个8-bit输入符号,经过编码后输出224个8-bit符号。通过32×32的交织器,使得编码流更加随机,增强了抗干扰能力。随后,这些编码数据进入卷积码编码阶段,使用的是CC(3, 1, 7)编码器,其生成多项式为(1338, 1718, 1658),基本码率为1/3,可产生不同码率的内码。

为了提高解码速度,本文采用了基于Viterbi算法的8路并行卷积译码结构,这大大提升了译码速率,同时降低了延迟。卷积码的解码输出经过解交织后,输入到里所码的译码器,这里采用的是基于RiBM(Restricted Boltzmann Machine)算法的里所码解码结构,以实现低复杂度的解码过程。

整个吉比特RS-CC级联译码器的设计包括8个独立的CC(3, 1, 7)译码器、一个32×32解交织器以及一个RS(224, 208)译码器。这种架构能够在TSMC 0.13 μm CMOS工艺下实现高效的硬件实现,其能效为0.135 nJ/bit,占用面积为5.19 mm2,同时提供了高达2 Gb/s的数据吞吐率,满足了高速无线通信的需求。

该设计结合了里所码的强纠错能力和卷积码的高速解码特性,为60-GHz无线个域网提供了一种高效、可靠的编码解码解决方案,对于提升系统的整体性能和鲁棒性具有重要意义。

107 浏览量

10096 浏览量

1480 浏览量

1327 浏览量

2024-11-02 上传

1135 浏览量

1692 浏览量

364 浏览量

194 浏览量

weixin_38714653

- 粉丝: 3

最新资源

- 掌握ACCESS 2000操作与数据库共享技巧

- Android中文API合集第七期翻译成果分享

- VB图片浏览器制作教程及源码分享

- C++开发的楼盘销售管理系统概述

- Crank.js:使用JSX编写高效且简洁的React风格组件

- MFC内存管理与调试技巧深入解析

- LSB算法在BMP图像信息隐藏与提取中的应用

- 打造类似携程的强效日期选择器JavaScript特效

- 精通MySQL4数据库管理与维护教程

- Android动态绘制图表:折线、圆柱、饼状图实现

- 自适应宽度的个性化下拉选择框实现

- 在Windows上实现Mac风格的Stack特效工具

- Chimee:构建强大视频播放功能的跨平台框架

- 动态清明上河图屏保:古典艺术的现代演绎

- MapGIS到ArcGIS SHP格式转换解决方案

- 全面掌握ACCESS 2000操作与数据库管理培训教程