MAX10高速LVDS I/O设计与实现指南

版权申诉

79 浏览量

更新于2024-06-28

1

收藏 1.28MB PDF 举报

“MAX 10 高速LVDS IO 用户指南.pdf”是INTEL MAX10 FPGA系列的数据手册,详细介绍了如何在MAX 10 FPGA中使用高速LVDS(Low Voltage Differential Signaling)输入/输出接口。该指南涵盖了LVDS I/O的设计概述、架构、功能、设计实现以及调试和故障排除。

1. **MAX10高速LVDS I/O设计概述**

- Altera SoftLVDS实现提供了灵活的高速通信解决方案。

- 设计者需要理解LVDS I/O在MAX10 FPGA中的体系结构和性能特性。

2. **MAX10高速LVDS架构与功能**

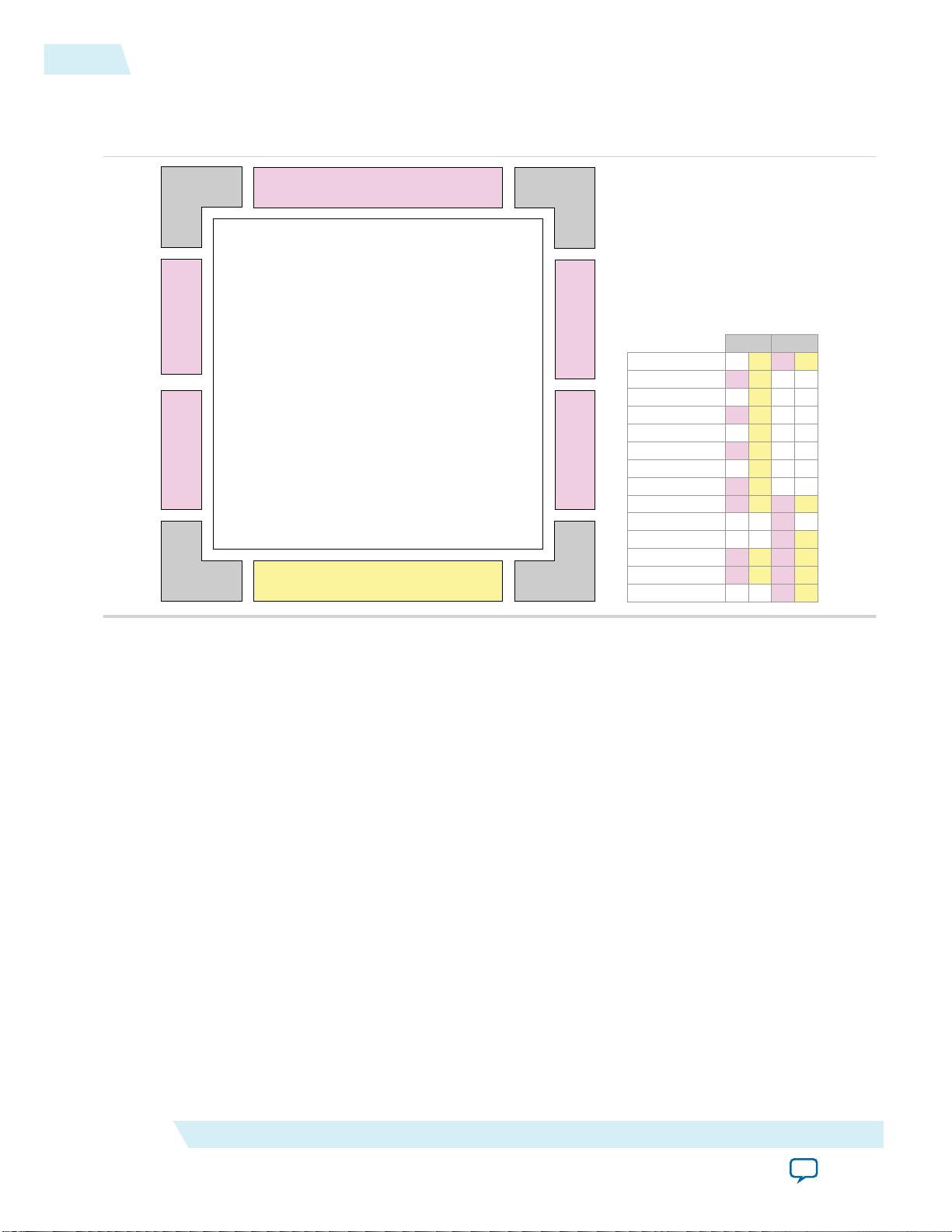

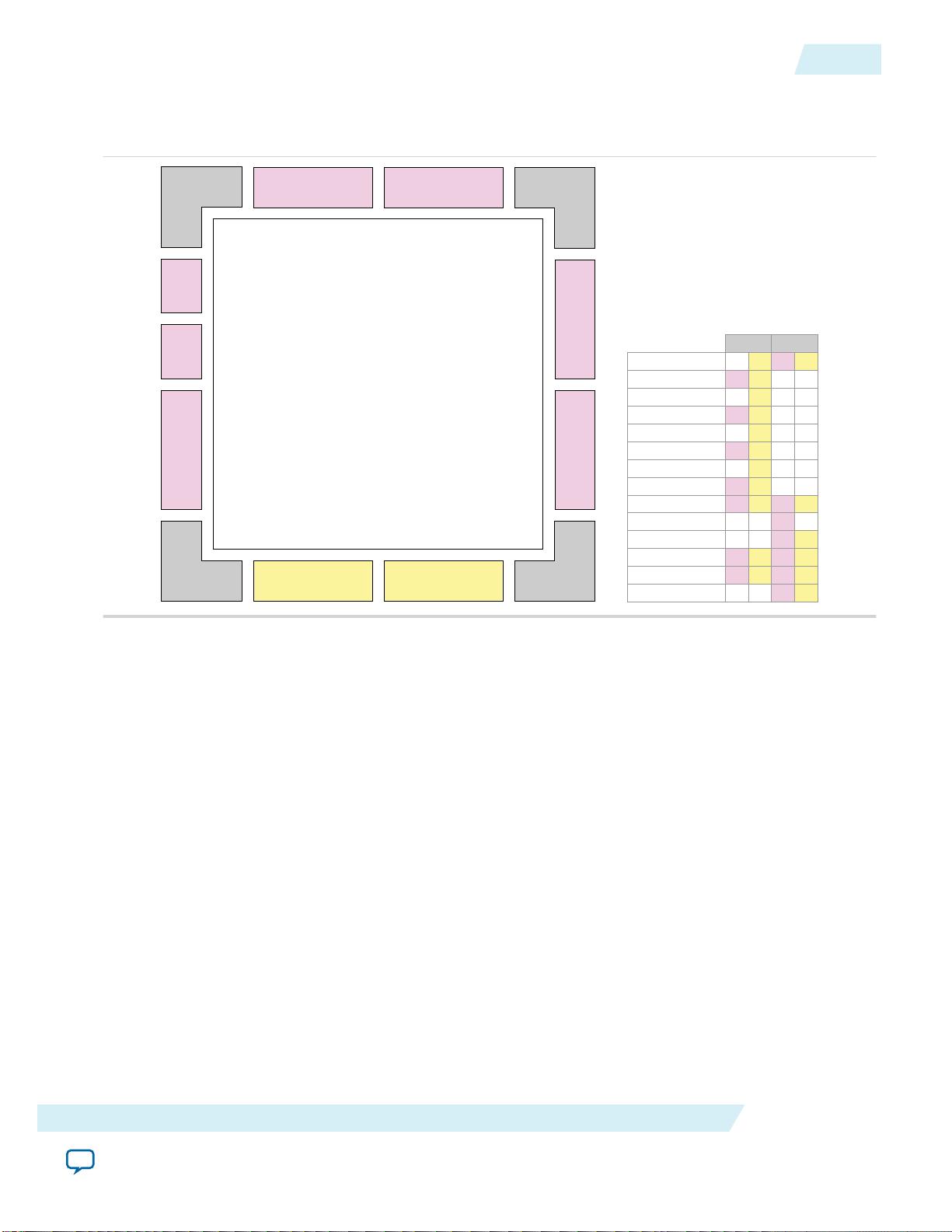

- LVDS通道支持:MAX10 FPGA可以配置为支持多种LVDS标准,如LVDSSERDES。

- I/O分布:LVDS I/O分布在高速和低速区域,低速区域的差分I/O管脚也有特定用途。

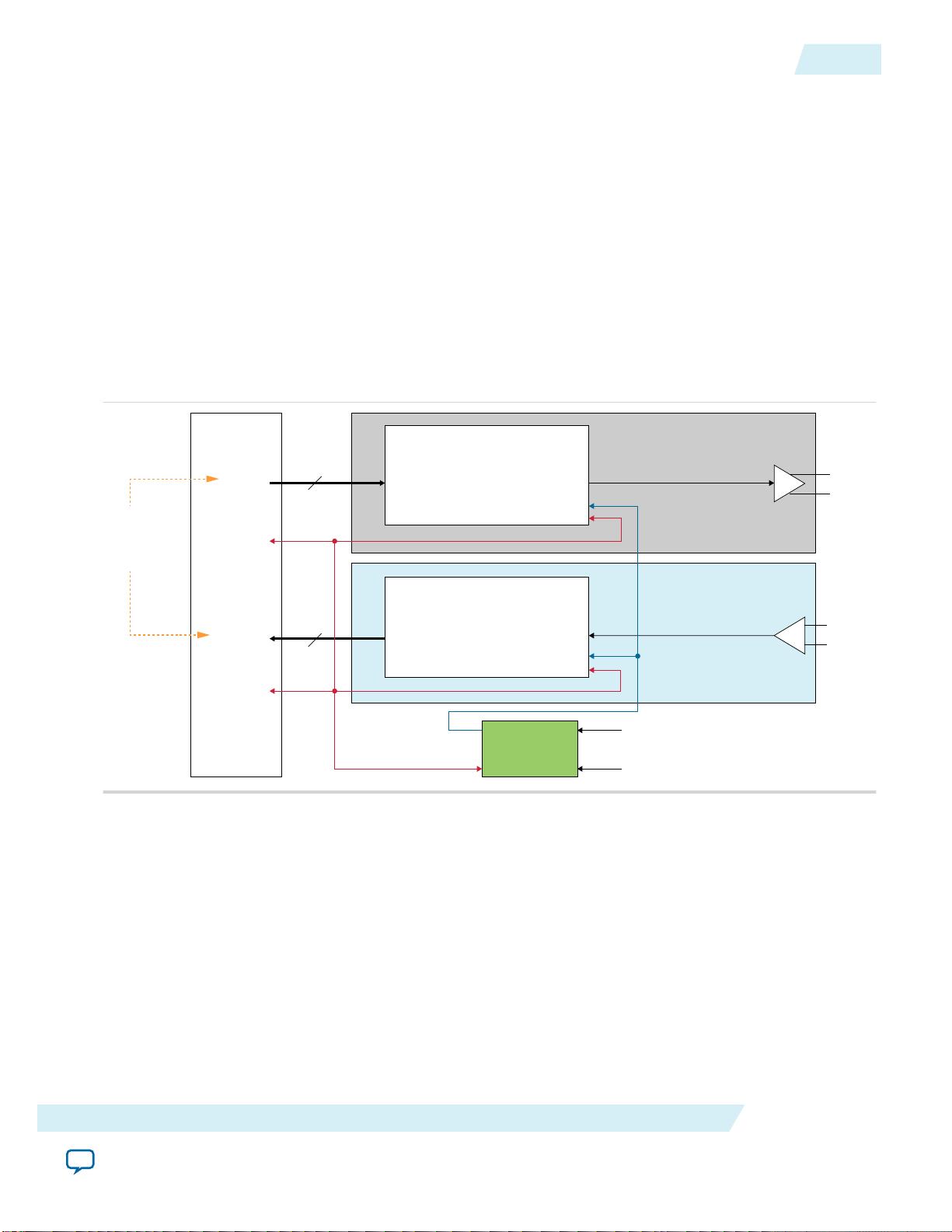

3. **LVDS发送器设计**

- 高速I/O发送器电路:描述了LVDS发送器内部电路的工作原理。

- 可编程预加重:允许用户根据线路条件调整信号上升时间,优化信号完整性。

- I/O匹配方案:提供了外部匹配网络的设计指导,以减少信号反射和提高信号质量。

4. **LVDS发送器FPGA设计实现**

- Altera SoftLVDS IP内核:用于在FPGA中实现LVDS发送器功能。

- 高速I/O时序裕量:确保满足时序要求,避免数据丢失或错误。

- 布局布线指南:包括通道、PLL和逻辑布局的建议,以优化信号路径。

5. **LVDS发送器调试和故障排除**

- RTL仿真:在硬件调试前进行,验证逻辑设计的正确性。

- 规则检查:基于几何和物理的规则确保设计符合制造和操作要求。

6. **LVDS接收器设计**

- 高速I/O接收器电路:包括软核解串器和数据重对齐模块,以适应不同速率和同步需求。

- I/O匹配方案:针对各种LVDS标准提供外部匹配指导,以确保信号的稳定接收。

7. **LVDS接收器FPGA设计实现**

- Altera SoftLVDS IP内核在接收器模式下的应用。

- 高速I/O时序裕量:同样适用于接收端,确保数据正确捕获。

8. **LVDS接收器调试和故障排除**

- 悬空输入管脚处理:指导如何正确处理未使用的LVDS输入,防止噪声引入。

- 时序约束:确保接收器满足时钟和数据同步的时序要求。

这份用户指南是工程师在利用MAX 10 FPGA实现高速LVDS通信时的重要参考资料,它提供了从设计到实现再到调试的全方位指导,有助于提升系统性能并降低开发风险。

2022-11-29 上传

270 浏览量

145 浏览量

2023-02-08 上传

GJZGRB

- 粉丝: 2969

- 资源: 7735

最新资源

- GDI方式实现图片拼接-易语言

- django-project-template:模板personalizado para criar novos projetos com o framework Django

- 安卓双机(两个手机)wifi下socket通信(client输入,在server端显示)

- 我的figma设计

- 手机端PC端视频播放

- javaScript-quiz-app:来自定义数组的应用显示问题

- JS+CSS+Bootstrap+PHP学习帮助文档chm.zip

- Denwa Click-To-Call-crx插件

- yeoman-coffee-jade-template:带有 grunt、coffee、jade、livereload 和其他一些实用程序的 Webapp 前端模板

- sevhou.github.io:个人网站

- html-css-toboolist

- Solar-System:虚拟太阳系

- TestThreadApp.rar

- 易语言gdi+实现拼接图片-易语言

- Dedup Tabs-crx插件

- 迅捷fw300um无线网卡驱动 官方最新版