Xilinx ISE9.1软件:模16计数器设计教程

需积分: 25 179 浏览量

更新于2024-07-28

收藏 1.16MB PPT 举报

"这篇教程介绍了如何使用Xilinx公司的ISE10.1软件进行简单的硬件描述语言(HDL)设计流程,包括创建项目工程、编写VHDL代码、设计编译、仿真测试以及设计文件的下载步骤。教程以设计一个模16计数器为例,详细阐述了每个操作环节。"

在电子设计自动化(EDA)领域,Xilinx ISE(Integrated Software Environment)是用于开发基于Xilinx FPGA(Field-Programmable Gate Array)和 CPLD(Complex Programmable Logic Device)的设计工具。版本10.1是该软件的一个早期版本,尽管现在可能已被更新的Vivado或Spartan等工具取代,但它仍能提供基础的FPGA设计经验。

1. **启动软件**: 首先,你需要启动ISE9.1的Project Navigator,这是软件的主界面,用于管理项目和设计流程。

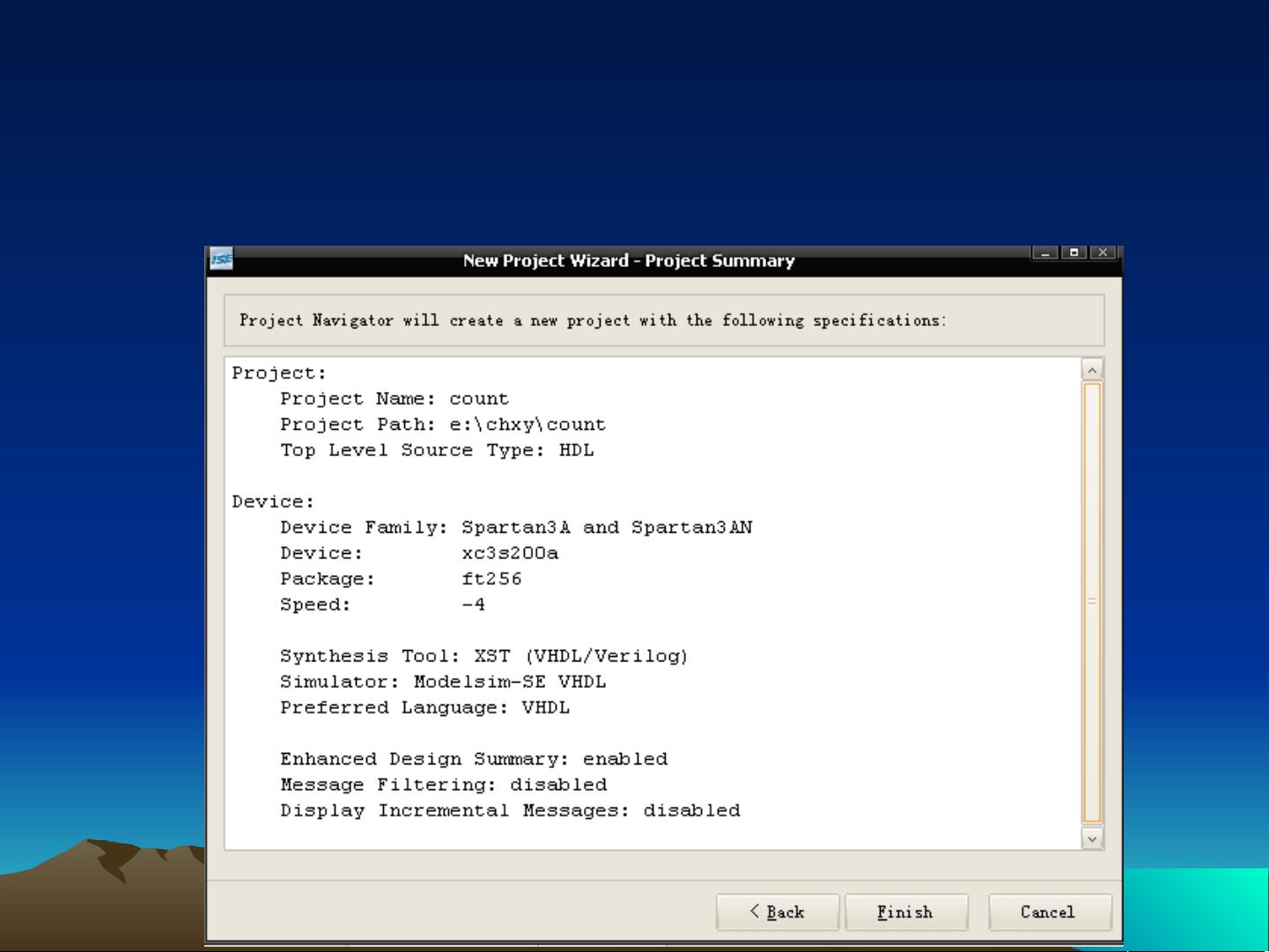

2. **创建项目工程**: 在"File"菜单中选择"New Project",并指定项目名称和保存位置。项目文件名应避免使用中文和数字开头,以防止潜在问题。

3. **设置参数**: 在新建项目向导中,你需要配置项目的基本参数,如目标设备、技术节点和其他相关设置。

4. **添加设计源**: 通过"Project"菜单的"New Source"选项,可以创建新的设计文件,通常选择VHDL或Verilog作为设计语言。

5. **编写VHDL代码**: 这里以VHDL为例,编写了一个模16计数器的代码。代码中定义了一个实体`cnt16`,具有输入时钟`clk`,输出模16数据`dout`和1Hz信号`dclk1`。`Behavioral`架构中包含了过程`process(clk)`,用于实现计数逻辑。

6. **设计编译**: 完成代码编写后,需要进行编译以检查语法错误和逻辑问题。在ISE中,可以通过"Build Design"或使用快捷键来编译整个项目。

7. **设计仿真**: 在确保编译无误后,可以进行设计仿真,验证设计功能是否符合预期。ISE提供了一套综合的仿真工具,如ISim,用于运行测试激励并查看波形结果。

8. **适配与下载**: 一旦设计被验证无误,就可以进行适配(Place & Route),这一步会决定逻辑单元在FPGA内部的具体布局和布线。最后,将生成的比特流文件下载到目标硬件,通常是通过JTAG接口进行编程。

这个教程通过一个具体的模16计数器实例,详尽地展示了使用ISE10.1进行FPGA设计的基本步骤。虽然现在的FPGA设计工具可能有所不同,但基本的设计流程——创建项目、编写代码、编译、仿真和下载——仍然是核心部分,对于学习FPGA设计概念是非常有价值的。

点击了解资源详情

点击了解资源详情

点击了解资源详情

114 浏览量

2021-12-13 上传

2021-11-24 上传

2021-10-07 上传

2021-10-07 上传

2021-12-13 上传

roronoa6781

- 粉丝: 0

- 资源: 1

最新资源

- 基于YOLO神经网络的实时车辆检测代码

- TravelAdvisor

- uiGradients-Viewer-iOS::artist_palette:一个开放源代码应用程序,用于查看https上发布的渐变

- 15套动态和静态科技风光类PPT模板-共30套

- Tonite

- 正点原子精英Modbus_Master_Template.zip

- 聚合物制造:移至Polymertools monorepo

- AboutMe

- Trello克隆

- IT资讯网_新闻文章发布系统.rar

- Simple Math Trainer Game

- igloggerForSmali

- Tomate

- 4,STM32启动文件.rar

- pghoard:PostgreSQL备份和还原服务

- hw9