XILINX FPGA配置流程详解

"XILINX FPGA硬件设计总结"

Xilinx FPGA的配置流程是其硬件设计中的关键环节,涉及多个步骤以确保正确无误地加载和启动逻辑功能。以下是详细的配置流程概述:

1. **设置阶段**:

- **复位开始**:在上电或通过外部PROG_B引脚触发低脉冲,FPGA进入复位状态。上电复位模块确保FPGA在电压达到工作范围前保持复位。

- **初始化**:复位结束后,配置存储器的内容被清除,所有I/O端口除了配置接口外,都置为高阻态。INIT_B引脚被拉低,表明初始化开始,如果外部保持INIT_B低,FPGA将保持初始化状态。

2. **加载阶段**:

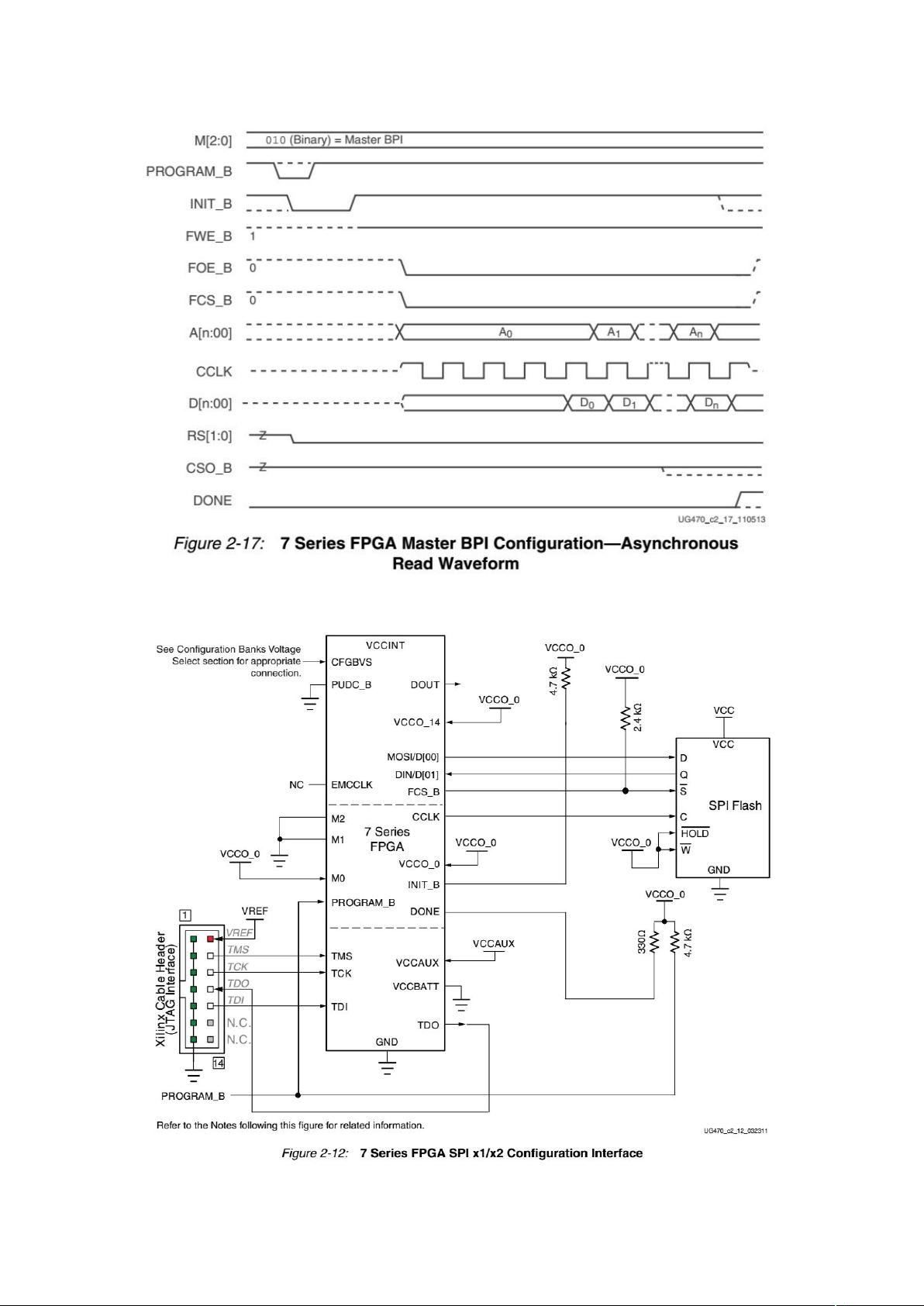

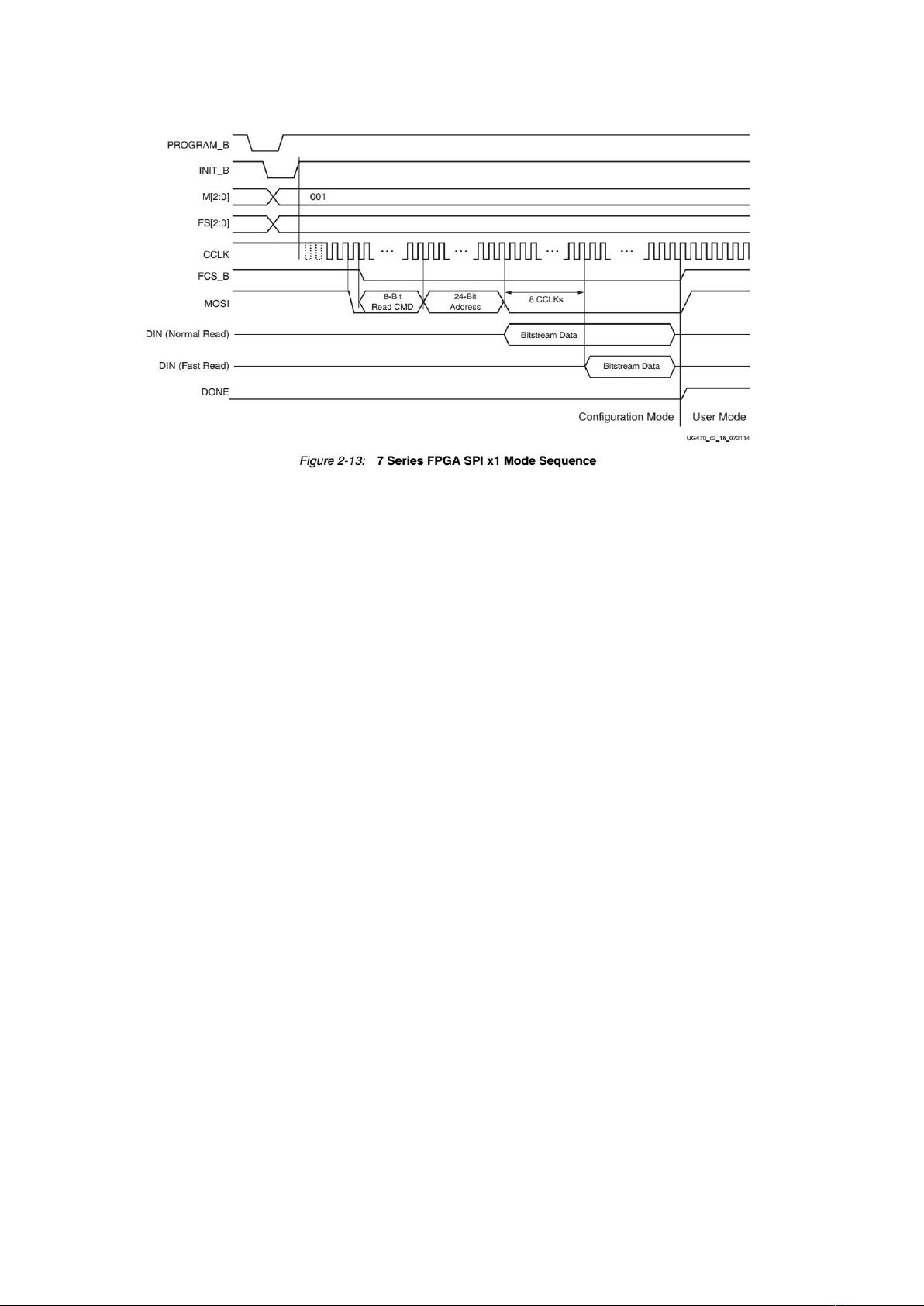

- **采样控制信号**:INIT_B恢复高电平,FPGA开始采样模式选择引脚M[1:0]和变量选择引脚VS。在主动模式下,CCLK有效,VS仅在主动BPI和SPI模式中发挥作用。

- **同步化**:FPGA利用同步头(如Spartan3的AA995566)来定位配置数据的起始点,确保数据传输的准确性。

- **ID检查**:FPGA检查配置流中的器件ID,与自身ID对比,防止配置错误的器件。28位特征值和4位掩码包含厂商、器件家族和规模信息。ID匹配失败时,ID_Err标志会被置高。

3. **启动内容加载**:

- **配置数据加载**:ID检查成功后,FPGA开始加载配置数据,这些数据定义了FPGA内部逻辑的连接和功能。

- **CRC校验**:在加载过程中,FPGA执行CRC校验以确认数据的完整性。任何帧数据的CRC错误会导致配置终止,INIT_B被拉低。

4. **启动序列**:

- **启动事件**:配置完成后,FPGA进入启动序列,依次释放DONE引脚、激活I/O和启动写使能。启动顺序可根据BitGen参数定制以适应不同应用场景。

Xilinx 7系列FPGA在此基础上可能有特定的配置模式和优化,但基本的配置流程与上述描述一致。理解这个过程对于调试、验证和优化FPGA设计至关重要,因为正确的配置是确保FPGA正常工作的前提。在设计中,必须注意每个步骤的细节,例如信号的时序、同步头的匹配以及错误检测机制,以确保可靠性和稳定性。

点击了解资源详情

点击了解资源详情

点击了解资源详情

106 浏览量

116 浏览量

2023-02-27 上传

2022-10-27 上传

2021-10-11 上传

2022-11-02 上传

qq_16662783

- 粉丝: 0

- 资源: 1

最新资源

- Angular实现MarcHayek简历展示应用教程

- Crossbow Spot最新更新 - 获取Chrome扩展新闻

- 量子管道网络优化与Python实现

- Debian系统中APT缓存维护工具的使用方法与实践

- Python模块AccessControl的Windows64位安装文件介绍

- 掌握最新*** Fisher资讯,使用Google Chrome扩展

- Ember应用程序开发流程与环境配置指南

- EZPCOpenSDK_v5.1.2_build***版本更新详情

- Postcode-Finder:利用JavaScript和Google Geocode API实现

- AWS商业交易监控器:航线行为分析与营销策略制定

- AccessControl-4.0b6压缩包详细使用教程

- Python编程实践与技巧汇总

- 使用Sikuli和Python打造颜色求解器项目

- .Net基础视频教程:掌握GDI绘图技术

- 深入理解数据结构与JavaScript实践项目

- 双子座在线裁判系统:提高编程竞赛效率