FPGA数字跑表设计与VHDL实现

版权申诉

62 浏览量

更新于2024-07-03

1

收藏 1.8MB DOCX 举报

"基于FPGA数字跑表的设计文档主要涵盖了基于FPGA的VHDL设计流程,以及电子秒表的单元电路设计,包括分频器、按键消抖、控制电路、计数器、寄存器、显示模块和使能模块等关键部分。报告详细介绍了从设计需求到系统实现的全过程,最后进行了测试和总结。"

在现代电子技术中,FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,常用于快速原型验证和定制化硬件设计。本报告重点讨论了使用FPGA实现数字跑表的设计,主要涉及VHDL语言和FPGA开发流程。

VHDL是硬件描述语言的一种,其特点是结构化和面向对象,既支持行为描述也支持结构描述,使得设计者可以清晰地描述数字系统的功能和结构。在1.1.1节中,VHDL的特点被提及,包括其强大的表达能力、可读性强、易于复用和仿真验证等优点。

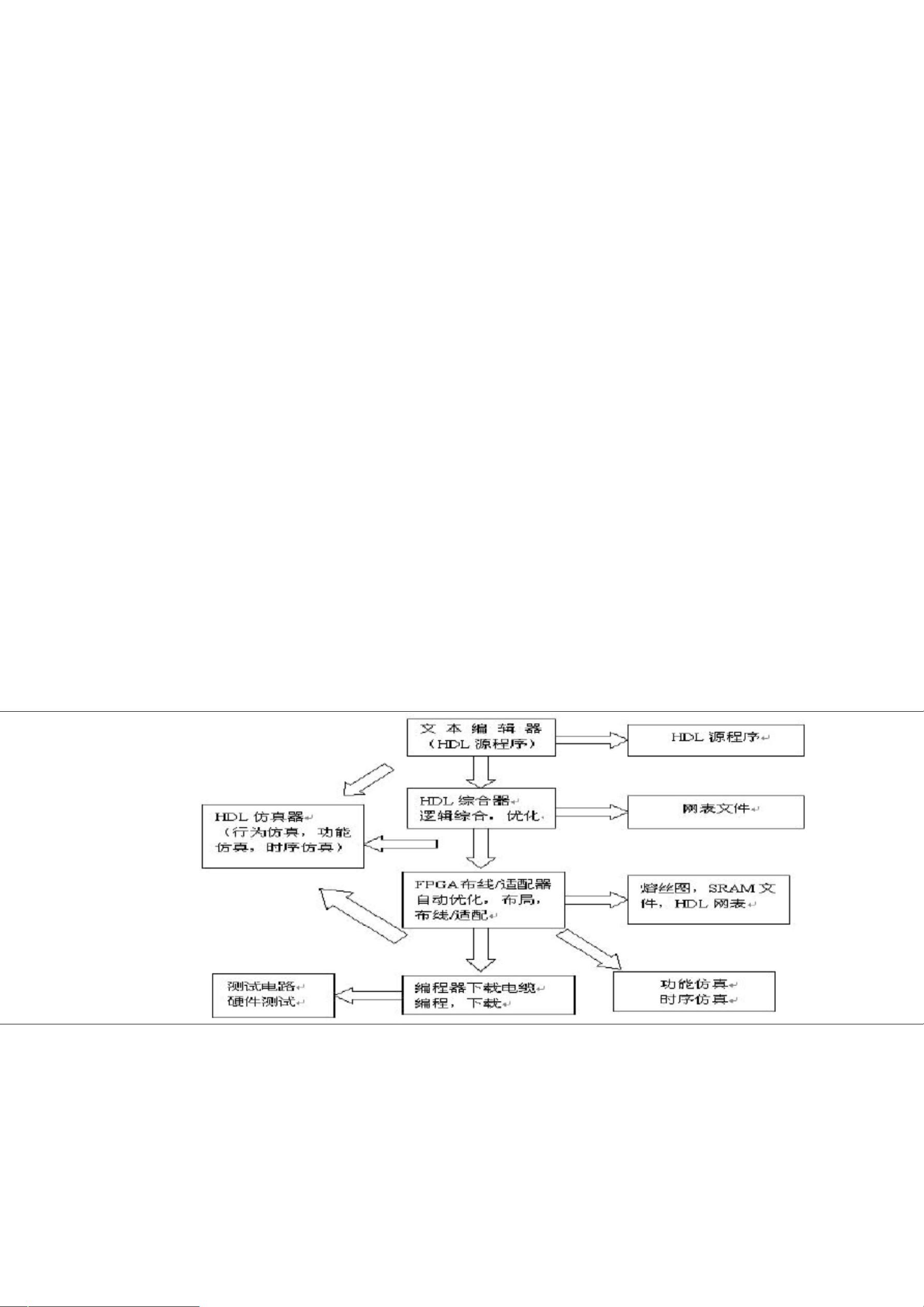

FPGA设计通常包括以下步骤:需求分析、逻辑设计、逻辑综合、布局布线和硬件测试。1.2.2节中提到了FPGA设计流程,开发者首先使用VHDL进行逻辑描述,然后通过软件工具进行逻辑综合,将高级语言转换成逻辑门级网表,接着进行布局布线,将逻辑门分配到FPGA的逻辑单元中,最后通过JTAG或SPI等接口下载到FPGA芯片上进行硬件验证。

在2.1节设计要求中,可能详细描述了数字跑表应具备的功能,如计时、暂停、复位、显示等功能。2.2节系统工作原理则可能解释了数字跑表如何通过计数器、控制电路和显示模块协同工作来实现这些功能。2.3节单元电路划分是将整个系统分解为可管理的部分,例如分频器用于产生精确的时间基准,按键消抖处理输入信号的稳定性,控制电路负责处理各种操作命令,计数器记录时间,寄存器存储当前时间,显示模块负责将时间信息转化为可视的七段数码管显示,而使能模块确保各个部分的正确同步。

在3.1节中,详细阐述了各单元电路的设计与分析,例如分频器通过降低输入频率来产生所需的计时脉冲;按键消抖电路则是为了避免因按键抖动导致的误操作;控制电路根据用户输入信号(如启动、暂停、复位)来控制计数器的增减;计数器采用加法计数或减法计数方式记录时间;寄存器用来存储当前的时间值;显示模块将这些数值转换为七段数码管可以显示的格式;使能模块则确保在正确的时间点更新显示。

4.1节的顶层设计整合了所有单元电路,确保它们协调工作,4.2节分配引脚和下载实现涉及到实际硬件连接和程序下载,而4.3节的测试结果和结论则评估了设计的性能和有效性。

在最后的5.1节经验及收获中,作者可能分享了在设计过程中遇到的问题、解决方法以及从项目中学到的技能和知识,这对于后续的FPGA设计是非常宝贵的经验积累。这个报告提供了一个完整的基于FPGA的数字跑表设计案例,对于学习FPGA设计和VHDL编程的读者来说具有很高的参考价值。

542 浏览量

1556 浏览量

301 浏览量

121 浏览量

2022-11-01 上传

G11176593

- 粉丝: 6927

- 资源: 3万+

最新资源

- SMTPSender(iPhone源代码)

- 类似瀑布流的网格视图效果

- win7 64位安装IE11所需补丁

- WIFIRobots

- 多路DA上位机+单片机源码.zip

- cace:CMS管理员命令执行

- cursoKuberneteswildfly:Curso cursoKubernetes野蝇sobre Cubernetes

- mysql-connector-java-8.0.25.zip

- 建筑节能平台登录网页模板

- 网络游戏-基于移动无线网络、通过远程服务器进行地图解析的方法.zip

- PCBMill:PCBMill FABtotum插件

- 房屋出租管理系统.rar

- Google Chrome:trade_mark:的标签管理器-crx插件

- WindowsFormsApp1.zip

- agora:面向目标的敏捷需求获取

- webtesting-ii-guided:Web测试II模块指导项目