TTL与CMOS与非门电路测试与应用解析

需积分: 42 142 浏览量

更新于2024-07-21

收藏 558KB PPT 举报

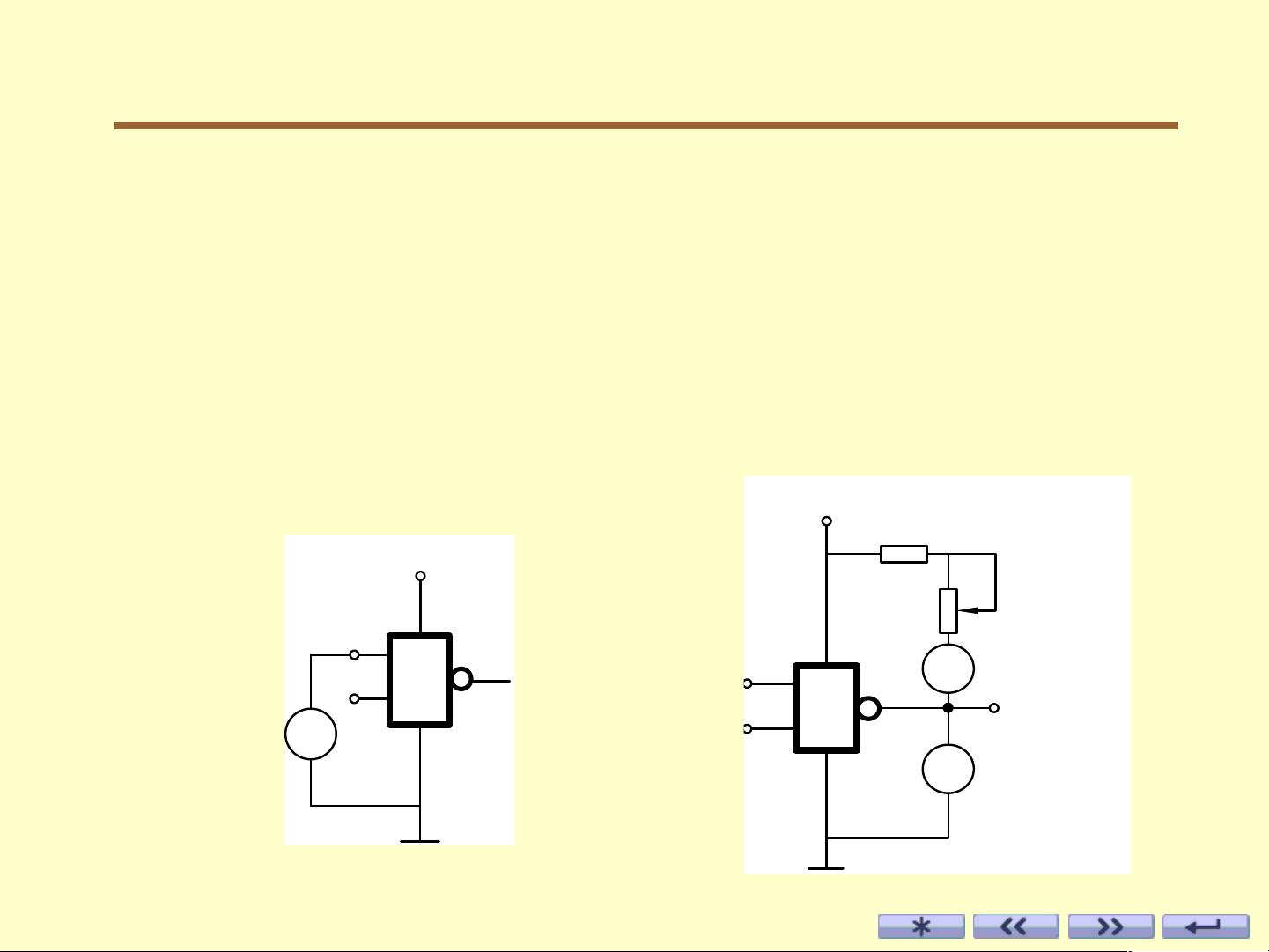

本资源主要涉及的是与非门的测试,包括TTL和CMOS逻辑电路芯片的使用,以及组合逻辑电路的功能测试方法。实验旨在让学习者掌握小规模集成电路(SSI)的设计方法。

在电子工程领域,与非门是一种基本的逻辑门,它的输出只有在所有输入均为高电平时才为低电平,否则输出为高电平。实验“与非门测试”分为两个部分,涵盖了TTL和CMOS两种常见的集成电路技术。

1. **TTL与非门电路**:

- **主要参数**:TTL与非门的关键参数包括静态功耗(PD)、输出高电平(VOH)、输出低电平(VOL)、扇出系数(NO)和平均传输延迟时间(tpd)等。

- **静态功耗**:PD要求不超过50mW。

- **输出电平**:VOH通常小于2.4V表示逻辑1,VOL低于0.4V表示逻辑0。

- **扇出系数**:NO表示门电路能驱动的最大输入电流,例如,如果IOL是输出端允许的最大灌电流,IIS是输入短路电流,则NO等于IOL/IIS。

- **传输延迟**:tpd是输入变化到输出响应一半所需的时间,通常在几纳秒至几十纳秒之间。

- **噪声容限**:VNH和VNL分别定义了输入电压的允许变化范围。

2. **TTL器件的使用规则**:

- **电源电压**:TTL电路通常需要+5V电源,允许误差范围为±10%。

- **电源滤波**:为了减少电流跳变引起的噪声干扰,应使用电容进行滤波,包括100μF的低频滤波电容和0.01μF至0.1μF的高频滤波电容。

- **输出端连接**:除了OC门和三态门,其他输出端不能直接连接到电源或接地。

3. **CMOS与非门**:

- CMOS与非门也有类似的参数,如输出电压水平和电源电压范围,但CMOS通常具有更低的功耗和更高的噪声免疫能力。

- 使用规则会有所不同,例如,CMOS电路更需要注意防止静电损伤,因为它们对静电非常敏感。

通过实验,学习者将熟悉如何利用这些逻辑门设计组合逻辑电路,这是数字系统设计的基础。组合逻辑电路是由多个逻辑门组成的,其输出仅取决于当前的输入状态,不具有记忆功能。理解这些基础知识对于设计和测试数字电路至关重要。

点击了解资源详情

点击了解资源详情

143 浏览量

2023-05-27 上传

2023-05-27 上传

duguzuyang

- 粉丝: 0

- 资源: 7

最新资源

- hello-webauthn

- 钢琴3D模型素材

- spec-prod:GitHub Action构建ReSpecBikeshed规范,验证输出并发布到GitHub页面或W3C

- xlsrange:从行号和列号生成一个excel范围-matlab开发

- C#使用Redis内存数据库

- XX公司组织架构说明书DOC

- 雨棚3d模型设计

- multiple-theme-switcher-website

- 电力及公用事业行业月报月全社会用电量同比增长长江三峡来水情况改善明显-19页.pdf.zip

- Conway's Game of Life:基于 Conway 的四个规则生成细胞群并研究其行为的接口。-matlab开发

- gulp:自己gulp练习

- 带反射面板的远距离光束中断传感器-项目开发

- 现代企业员工培训与开发的实施模型DOC

- lab-bucket-list

- 苹果专卖店三维模型设计

- jshelp:Javascript 帮助