优化ARM嵌入式系统CF卡接口:CPLD实现高速稳定存储

96 浏览量

更新于2024-08-29

收藏 294KB PDF 举报

"基于ARM的嵌入式系统CF卡存储技术"

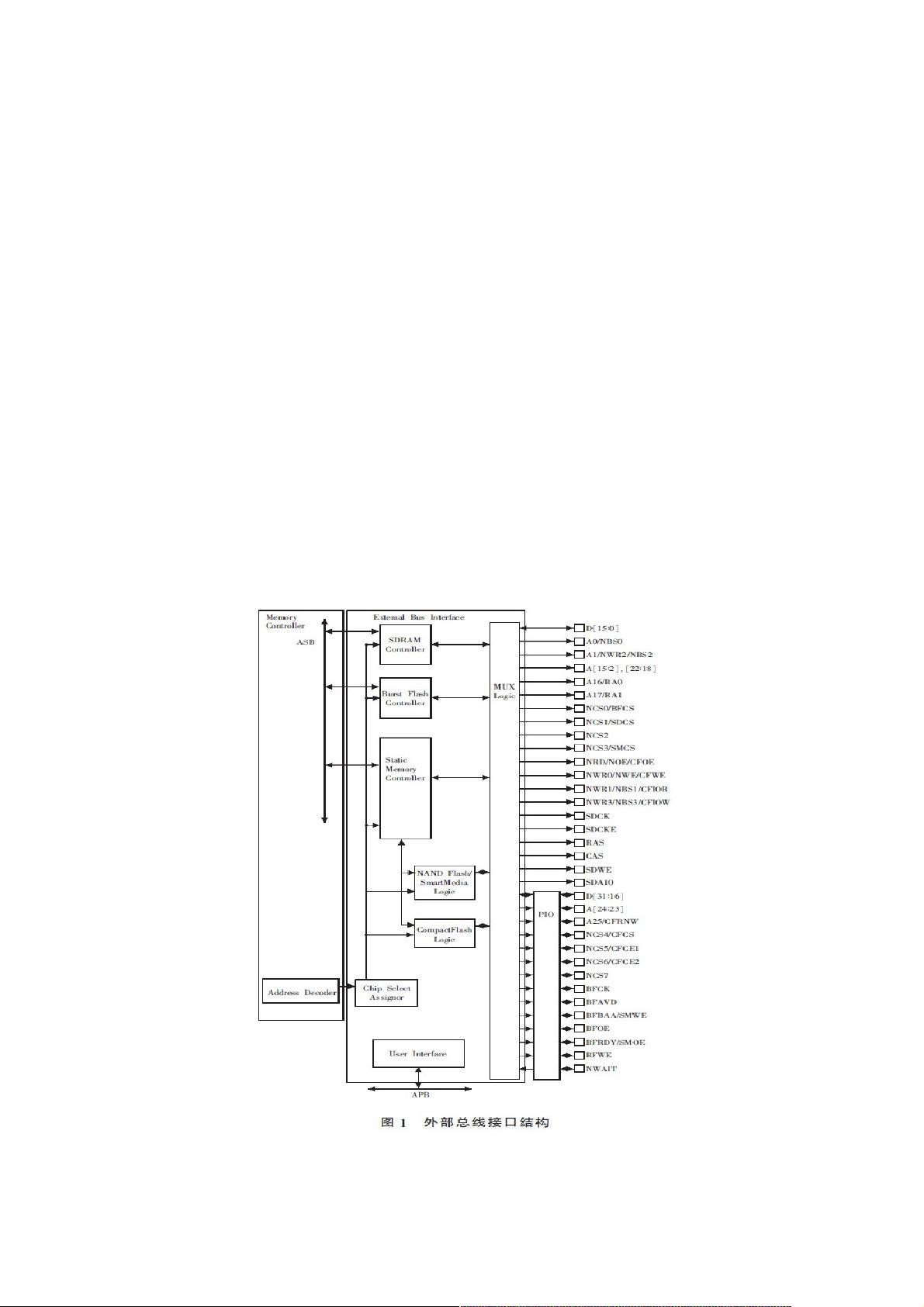

本文主要探讨了在嵌入式系统中,如何改进基于ARM处理器的CF卡存储技术,以解决现有接口电路的复杂性、稳定性差和速度慢的问题。文章以AT91RM9200这款基于ARM920T内核的处理器为例,深入研究了其外部总线接口(EBI)以及CF卡和可编程逻辑器件CPLD的工作原理。

首先,传统的CF卡接口电路通常包含双向缓冲器、与非门等多种逻辑器件,这增加了接口的复杂性,并可能导致稳定性问题。为了解决这些问题,作者提出了一个新的设计方案,即利用CPLD(复杂可编程逻辑器件)替代这些分立的逻辑组件。CPLD具有高度的灵活性,可以通过现场编程来实现不同的逻辑功能,因此可以简化接口电路,提高系统的稳定性和存储速度。

实验结果证实,新设计的CF卡接口电路不仅结构更简洁,而且在稳定性、灵活性和高速存储方面表现出显著优势,这对嵌入式系统的接口设计具有重要指导意义。特别是在嵌入式系统中,大容量存储需求日益增长,CF卡因其成本效益高、存储容量大、尺寸小巧和良好的兼容性而成为理想的存储解决方案。

文中还简要介绍了外部总线接口(EBI)的角色。EBI是AT91RM9200处理器与外部存储器和外设进行通信的关键组成部分,它支持多种存储卡协议,包括CF卡和SmartMedia,减少了对外部组件的需求,使得系统设计更为高效。EBI的高速特性使其能够适应高数据传输速率的应用场景,为嵌入式系统提供强大的扩展能力。

通过CPLD的灵活编程,开发者可以根据具体应用需求定制CF卡接口的逻辑,从而优化数据读写性能,提升系统整体效率。这种创新方法为未来嵌入式系统的存储设计提供了新的思路,尤其是在对存储速度和稳定性有高要求的应用中,如工业控制、物联网设备和移动通信设备等。

本文详细阐述了基于ARM的嵌入式系统中,如何通过CPLD优化CF卡接口电路,以实现更高效、稳定的存储性能。这种技术改进对于提升嵌入式系统的整体性能和可靠性具有重要意义,同时也为相关领域的工程实践提供了有价值的参考。

2020-10-21 上传

2023-05-29 上传

2023-07-28 上传

2023-05-24 上传

2023-06-10 上传

2023-12-22 上传

2023-04-29 上传

2023-09-25 上传

2023-09-10 上传

weixin_38500607

- 粉丝: 4

- 资源: 964

最新资源

- OptiX传输试题与SDH基础知识

- C++Builder函数详解与应用

- Linux shell (bash) 文件与字符串比较运算符详解

- Adam Gawne-Cain解读英文版WKT格式与常见投影标准

- dos命令详解:基础操作与网络测试必备

- Windows 蓝屏代码解析与处理指南

- PSoC CY8C24533在电动自行车控制器设计中的应用

- PHP整合FCKeditor网页编辑器教程

- Java Swing计算器源码示例:初学者入门教程

- Eclipse平台上的可视化开发:使用VEP与SWT

- 软件工程CASE工具实践指南

- AIX LVM详解:网络存储架构与管理

- 递归算法解析:文件系统、XML与树图

- 使用Struts2与MySQL构建Web登录验证教程

- PHP5 CLI模式:用PHP编写Shell脚本教程

- MyBatis与Spring完美整合:1.0.0-RC3详解