"计算机结构与逻辑设计强化班08级第七次课:时序逻辑电路测验评述"

版权申诉

20 浏览量

更新于2024-02-23

收藏 546KB PPT 举报

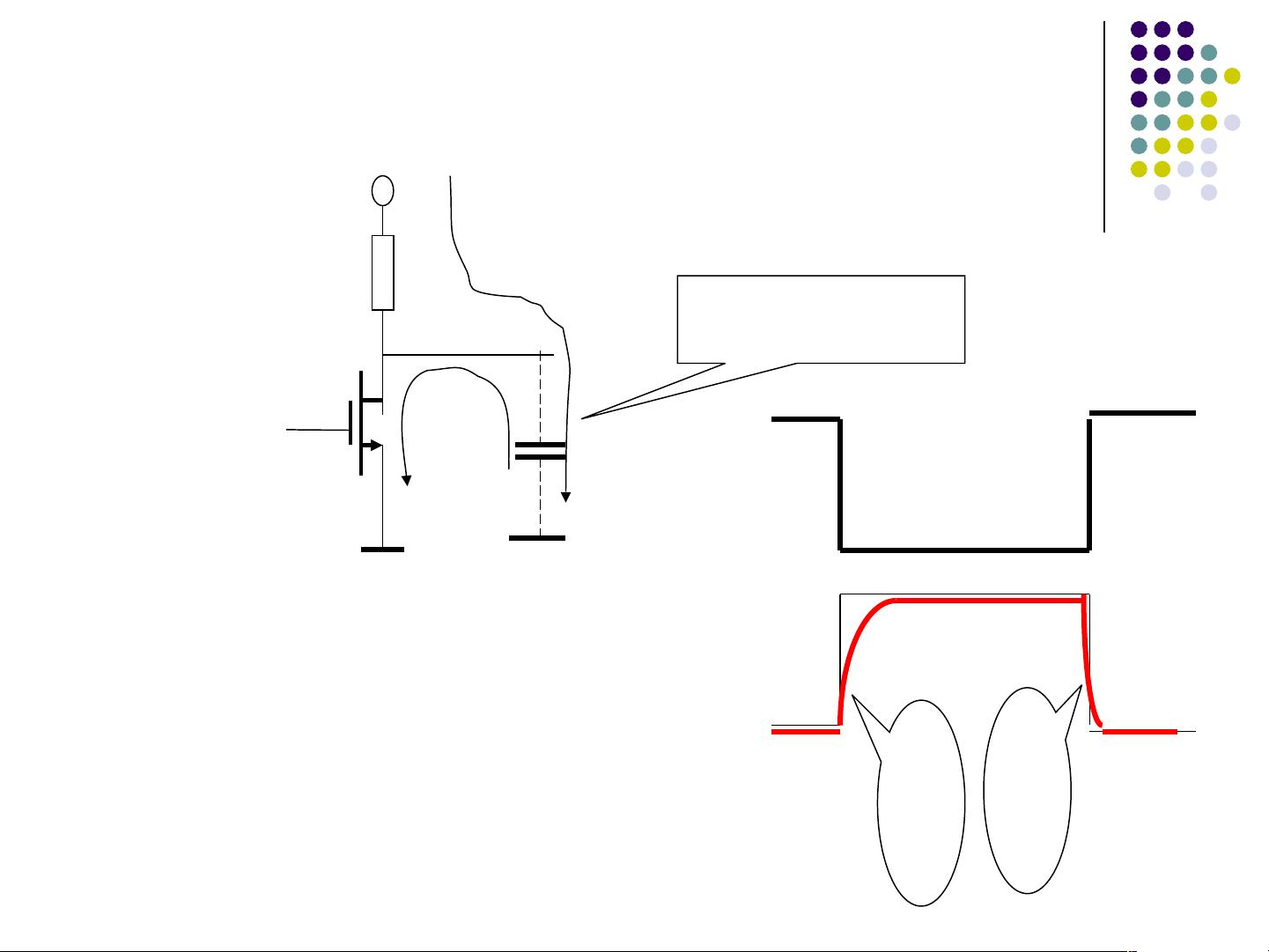

本次课程内容为计算机结构与逻辑设计的强化班第七次课,主要涉及时序逻辑电路。在课堂上进行了有关触发器输出波形S1D的绘制和评述。学生们在测试中出现了一些错误情况,例如对S、R功能不清楚,对时钟触发特性不清楚,将时钟的触发边沿弄反,以及在S、R作用以后,时钟作用沿到来之前的状态画得不对。通过评述测试结果,帮助学生们理解和强化这些概念和知识点。

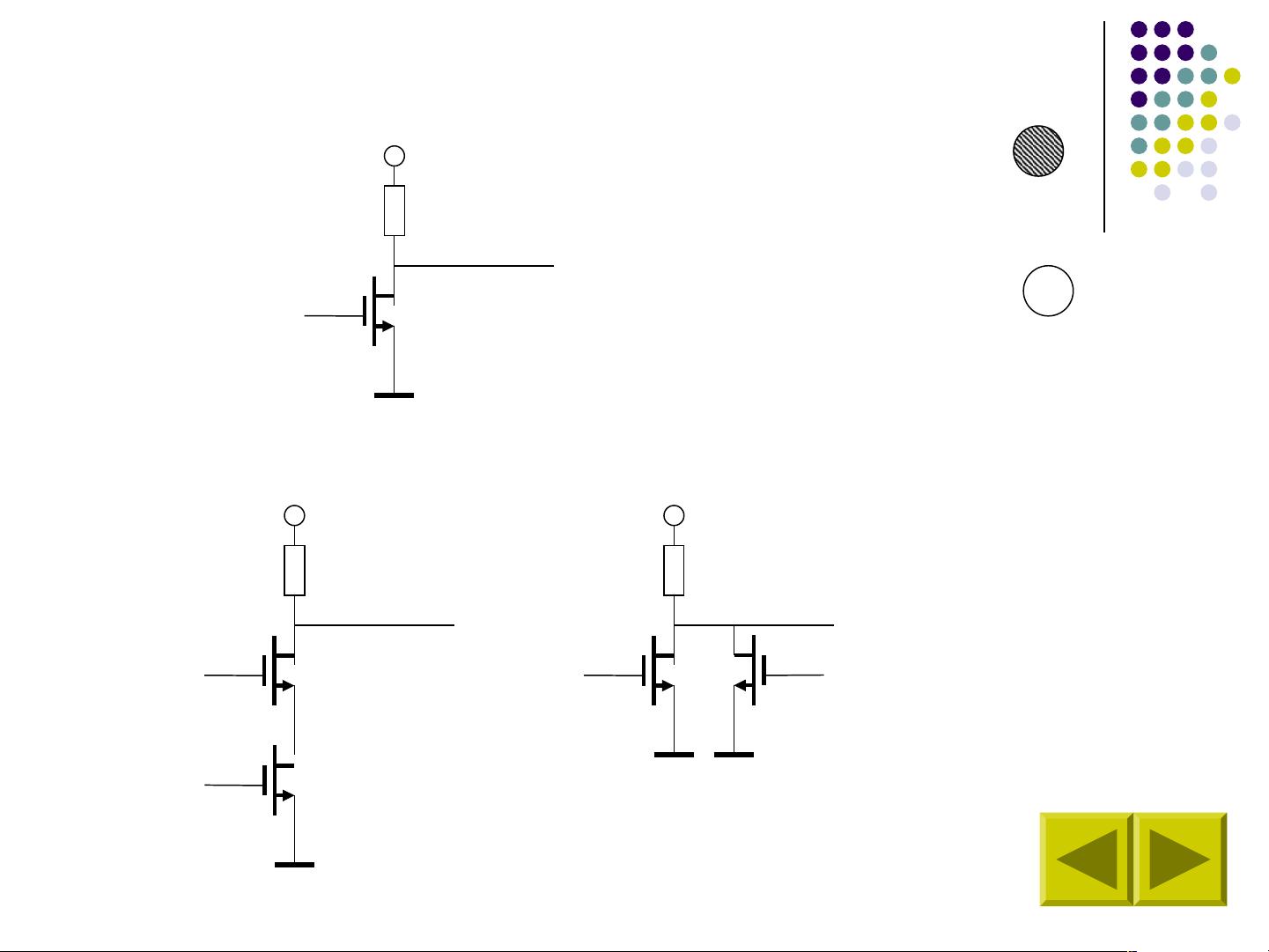

时序逻辑电路是计算机结构与逻辑设计中的重要内容,对于理解计算机内部工作原理和进行电路设计都具有重要意义。学生们在课程中学习了保持触发器的基本原理和方法,以及如何绘制和评述触发器的输出波形。通过对S、R、C、D、P和Q等信号的操作和触发,学生们逐渐掌握了时序逻辑电路的基本运行机制。

在测试评述中,发现学生们存在一些常见的错误情况,例如对S、R功能不清楚,有的甚至弄反了;对时钟触发特性也不清楚,导致状态随D信号变化。同时,也有学生将时钟的触发边沿弄反,导致绘制的波形不正确。这些错误情况需要及时指出和纠正,以帮助学生们加强对时序逻辑电路的理解和运用能力。

针对这些错误情况,课程进行了详细的评述和讲解。首先是对S、R、C、D、P和Q等信号的功能和作用进行了再次强调和阐述,帮助学生们更加清晰地理解它们之间的关系和操作规则。接着针对时钟触发特性的探讨,课程对每个时钟周期内状态的改变规律进行了详细说明,帮助学生们理解时钟对于时序逻辑电路的重要性和作用。同时,课程也详细分析了学生们在测试中出现的错误情况,并提出了一些避免和纠正这些错误的方法和建议,例如在S=R=0(保持)期间,没有时钟信号的有效边沿作用,状态就不改变。

此外,课程还对门电路实现高、低电平的原理和方法进行了介绍和讨论,帮助学生们理解和掌握电路中高低电平的实现原理。通过Uo=Vcc、Uo=Vcc-R1/R2、R2>R1、R2<R1等公式和原理的讲解,学生们对门电路的工作原理有了更加清晰的认识。

总的来说,本次课程对时序逻辑电路和触发器的原理和方法进行了深入的讲解和评述,帮助学生们增强了对这些知识点的理解和应用能力。通过测试评述,学生们对常见的错误情况有了更清晰的认识,并且增强了对正确操作和绘制输出波形的认识。这对于他们的学习和电路设计能力都具有重要意义,为他们在未来的学习和工作中打下了坚实的基础。同时,课程通过讨论门电路实现高低电平、电路中的常见错误以及纠正方法等内容,也帮助学生们增加了对电路设计和实现的认识,为他们的专业发展提供了有力支持。

综上所述,本次课程内容丰富、重点突出,通过绘制和评述触发器的输出波形,并详细分析测试评述结果,帮助学生们进一步加深了对时序逻辑电路和门电路的理解,为他们未来的学习和发展提供了有力的支持和帮助。同时,也为他们进行电路设计和实现提供了重要的指导和支持。相信随着不断的学习和实践,学生们的专业能力和技术水平会不断提高,为计算机领域的发展和创新做出更多的贡献。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-07-04 上传

2021-09-17 上传

2021-09-17 上传

2021-09-17 上传

wxg520cxl

- 粉丝: 25

- 资源: 3万+

最新资源

- 火炬连体网络在MNIST的2D嵌入实现示例

- Angular插件增强Application Insights JavaScript SDK功能

- 实时三维重建:InfiniTAM的ros驱动应用

- Spring与Mybatis整合的配置与实践

- Vozy前端技术测试深入体验与模板参考

- React应用实现语音转文字功能介绍

- PHPMailer-6.6.4: PHP邮件收发类库的详细介绍

- Felineboard:为猫主人设计的交互式仪表板

- PGRFileManager:功能强大的开源Ajax文件管理器

- Pytest-Html定制测试报告与源代码封装教程

- Angular开发与部署指南:从创建到测试

- BASIC-BINARY-IPC系统:进程间通信的非阻塞接口

- LTK3D: Common Lisp中的基础3D图形实现

- Timer-Counter-Lister:官方源代码及更新发布

- Galaxia REST API:面向地球问题的解决方案

- Node.js模块:随机动物实例教程与源码解析