SystemVerilog基础学习与实践指南

需积分: 13 190 浏览量

更新于2024-07-09

收藏 47.18MB PDF 举报

"SV基础学习资料,讲解系统Verilog的基础概念,包括数据类型、数组操作、字符串处理等,并强调实践的重要性。"

系统Verilog(SystemVerilog)是一种强大的硬件描述语言,广泛用于验证和设计电子系统。本资料主要针对SV的基础学习,通过类比C语言来解释一些基本概念。

在系统Verilog中,`byte` 类似于C语言的 `char`,都是8位。`int` 和 `integer` 都是32位,虽然名字较长,但它们都采用四值逻辑。值得注意的是,`byte` 的最高位用作符号位,正数为0,负数为1。

当8位的有符号数赋值给更宽的数据类型时,会进行扩展。例如,一个8位的负数赋值给9位的 `result_vec`,会先扩展一位,高位补1,形成16进制的 `h180`。而如果进行无符号转换,依然保持为8位的无符号数 `h80`,在扩展为9位时,高位补0,变为 `h080`。

在学习过程中,不要等到完全掌握所有理论才开始实践。一旦学到一定程度(如20%-30%),就应该尝试编写实验代码,以加深理解。

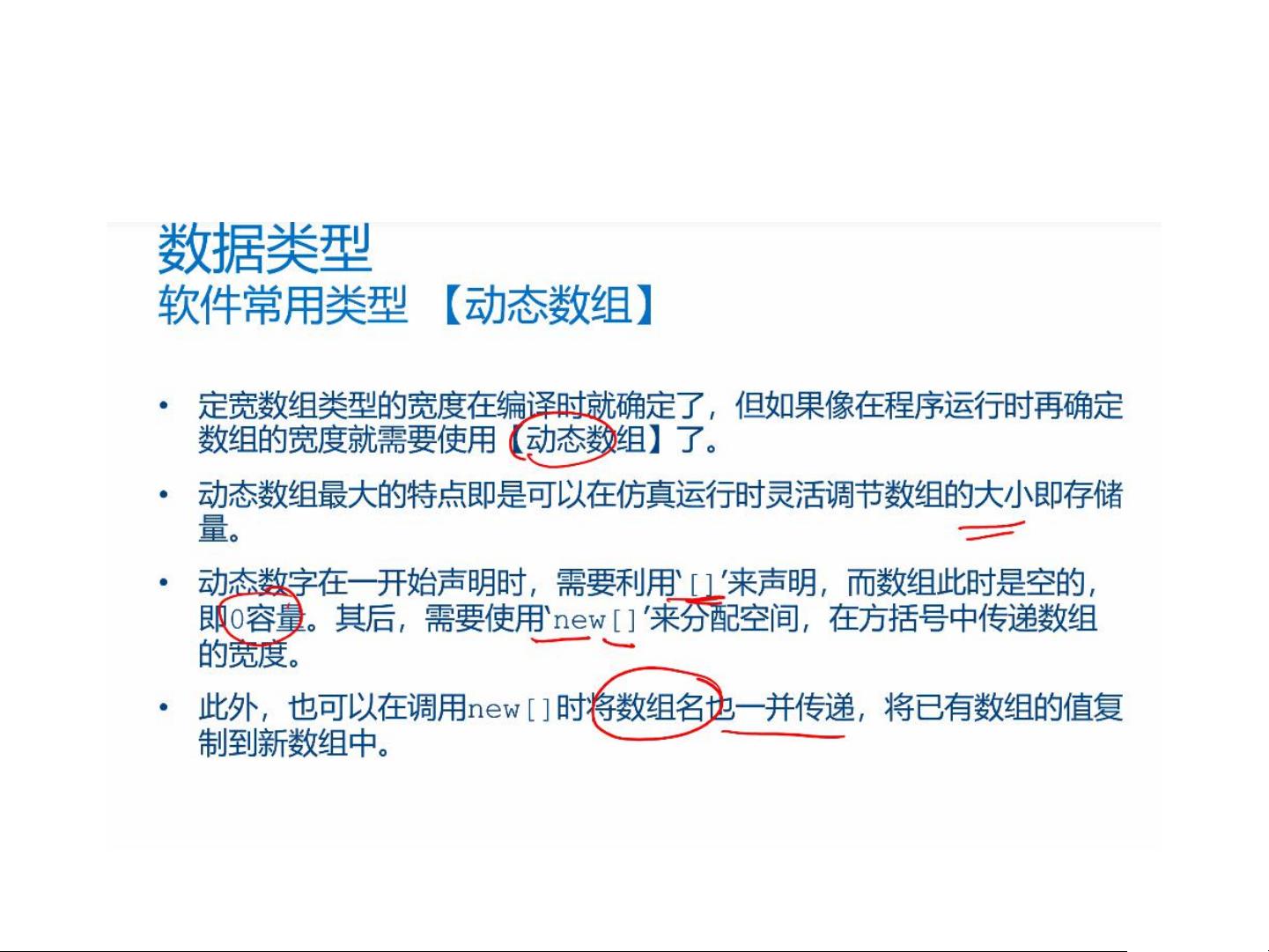

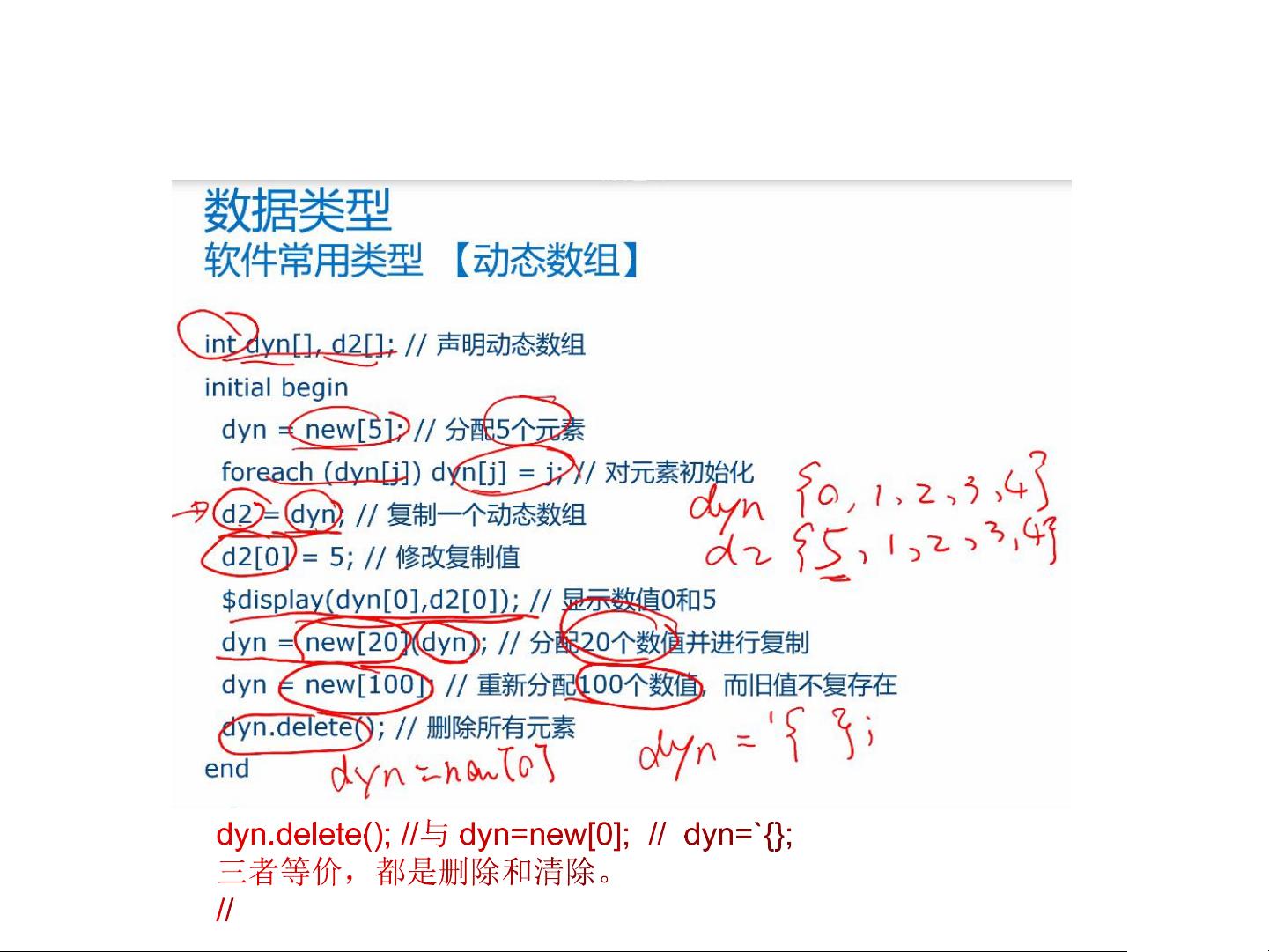

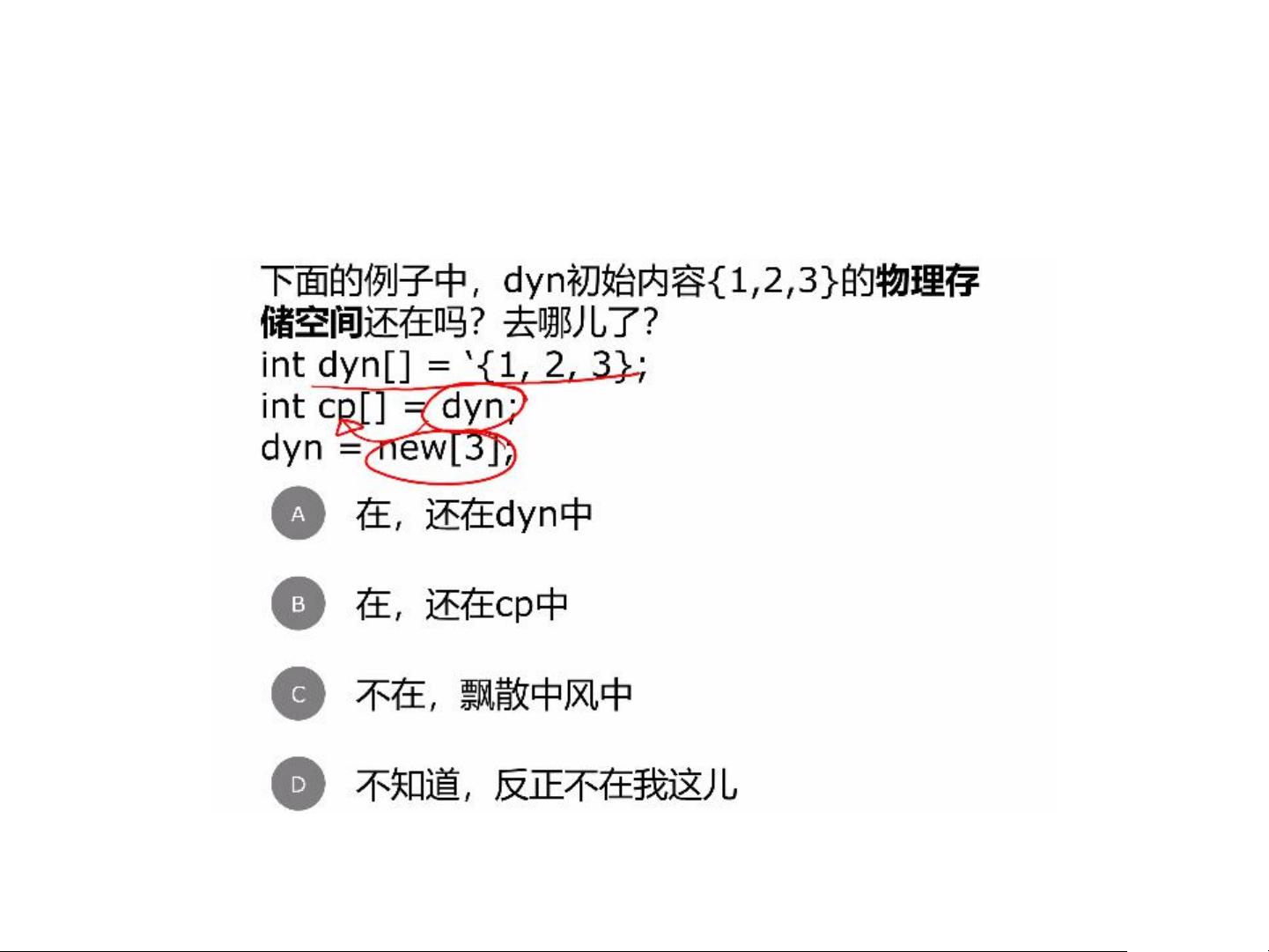

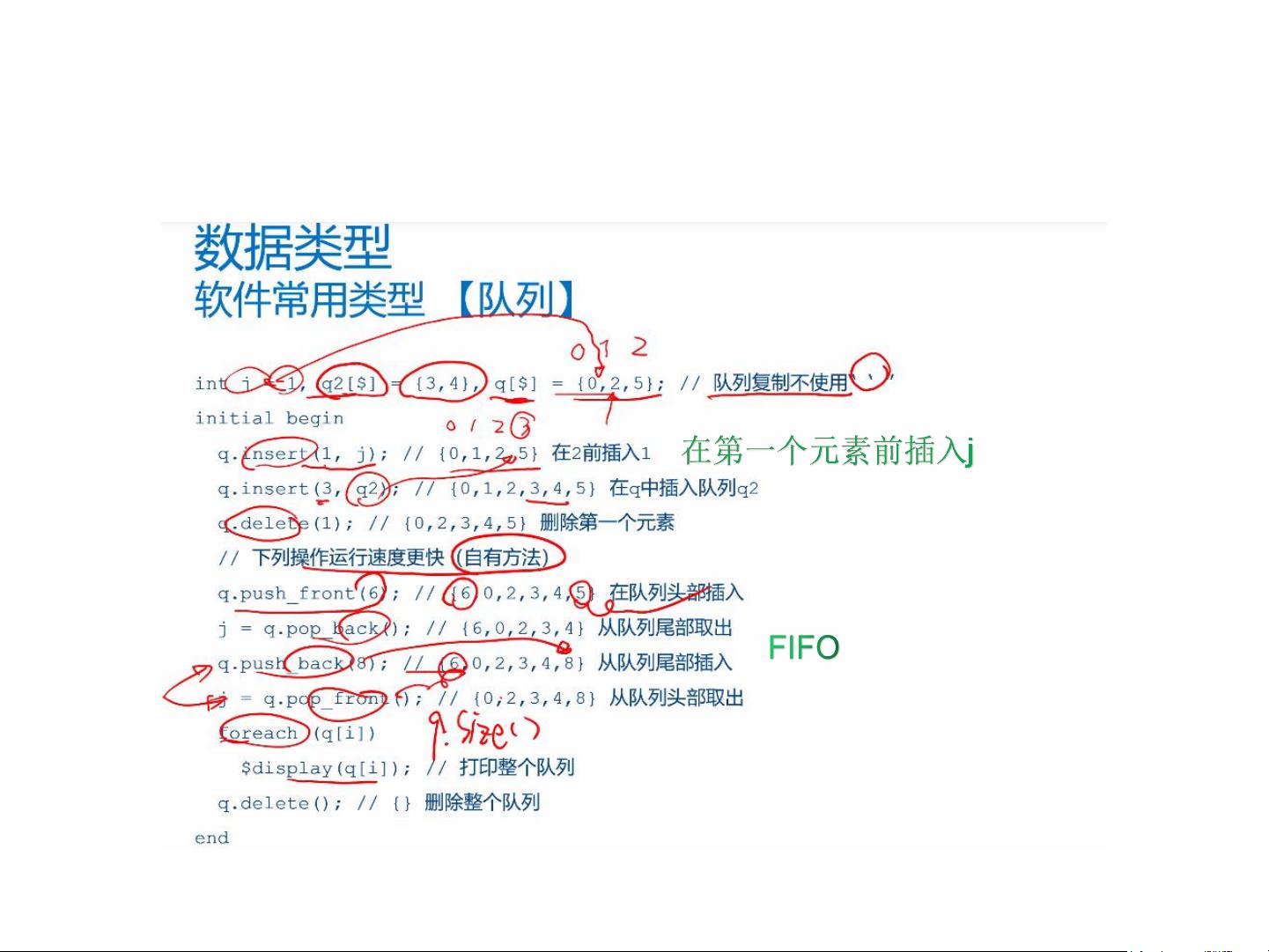

系统Verilog提供了一些特殊的数组操作。例如,`foreach` 循环在处理数组时特别方便。动态数组可以通过 `new[大小]` 来创建,如 `dyn=new[20](dyn)`,这会创建一个新的数组,并用旧数组的前5个元素填充新数组的低5位。对于数组的操作,如移位,`foreach` 循环可以简洁地实现连续移动。

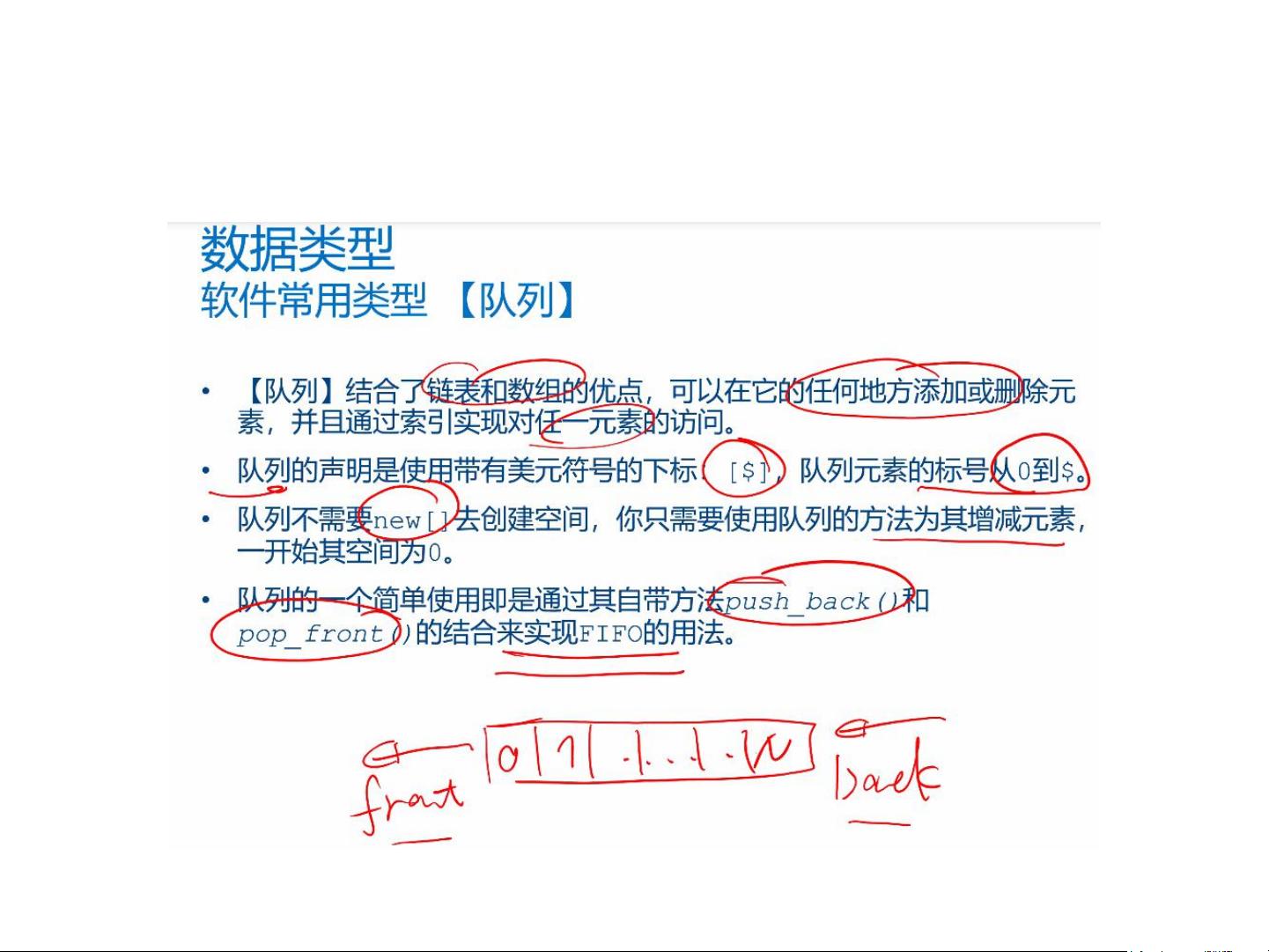

系统Verilog中的结构体允许我们定义包含多个变量的数据类型。例如,`struct {bit[7:0] r, g, b}` 声明了一个包含红、绿、蓝三个变量的匿名结构体。`pixel_s` 可以定义为这种类型的自定义变量。数组的赋值有两种方式,合并型数组(数据连续存放)使用反引号 `{}`,非合并型数组(如队列)使用花括号 `{}`。

字符串处理方面, `$sformatf()` 用于格式化字符串,`$display()` 用于打印字符串,类似于C语言的 `printf`。字符串的长度可以用 `len` 函数获取,不建议使用 `size`。`getc` 相当于 `getchar`,`putc` 类似 `putchar`。`tolower` 函数用于将字符转化为小写。`substr(2,5)` 可以提取字符串的一部分,从第2个字符到第5个字符(包括两端)。空字符串可以用 `{}` 定义,字符串拼接使用 `=` 符号,如 `s={"abc", "def"}`。字符串替换功能强大,可以替换指定位置的字符。

在系统Verilog中,`function` 通常用于表示逻辑电路,而 `task` 用于表示时序电路。函数的返回值可以是 `int` 类型,也可以直接写在参数列表中。尽量使用 `task` 调用来提高代码的可读性和可维护性。

这份资料详细介绍了系统Verilog的基本概念,提供了丰富的实例,帮助初学者快速理解和应用这个语言。实践是学习的关键,理论与实践相结合能更好地掌握系统Verilog的精髓。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-10-12 上传

2020-04-15 上传

2021-04-11 上传

小计地盘

- 粉丝: 0

- 资源: 9

最新资源

- Douban-Movie:仿豆瓣电影页面

- 电子功用-基于幅值调制视觉诱发电位脑-机接口方法

- ParallelRepastCore:将 RePast3 与并行模型一起使用的两个精简示例

- column-encryption:使用SQL Always Encrypted库演示列(字段)级加密模式的示例应用程序

- Python库 | ms_active_directory-1.10.1.tar.gz

- fabric::coat::socks:功能齐全的简约降价编辑器。 - 即将推出

- assignment3p1

- 亚马逊快速搜索-crx插件

- Python库 | mssql_dataframe-1.0.0.tar.gz

- pyca-cryptography

- bi-dashboard:有货数据可视化工具

- 淘客喵佣金猎手-crx插件

- gt_fsf_hw10_team_profile_generator:此分配要求我们利用节点js和相关的npm包根据用户输入创建一些特定HTML内容。 我们还必须使用npm Jest创建单元测试,并在演练视频中演示其功能

- CodeIdea:一些有用或好的代码可以解决我的问题

- Laravel_Ecommerce:电子商务代码逐步

- neilrathi.github.io:Github Pages网站