静态时序分析在集成电路设计中的应用

"这份文件是关于静态时序分析在逻辑设计和ASIC开发中的应用的深入学习资料。课程涵盖了静态时序分析的基本概念、目的、路径分析、方法、工具介绍以及如何解读时序分析报告和进行逻辑优化设计。"

在集成电路(ASIC)设计中,静态时序分析(Static Timing Analysis,简称STA)是一项至关重要的步骤,用于确定电路的运行速度和确定是否存在可能导致系统故障的时序问题。静态时序分析不依赖于模拟电路的行为,而是基于电路的逻辑门级描述来评估信号传播时间。

1. 静态时序的概念:它主要关注电路中的关键路径,这些路径决定了整个设计的最慢时序路径,即从时钟源到关键数据输入的最长路径。关键路径的延迟决定了芯片的时钟周期,进而决定了芯片的运行速度。

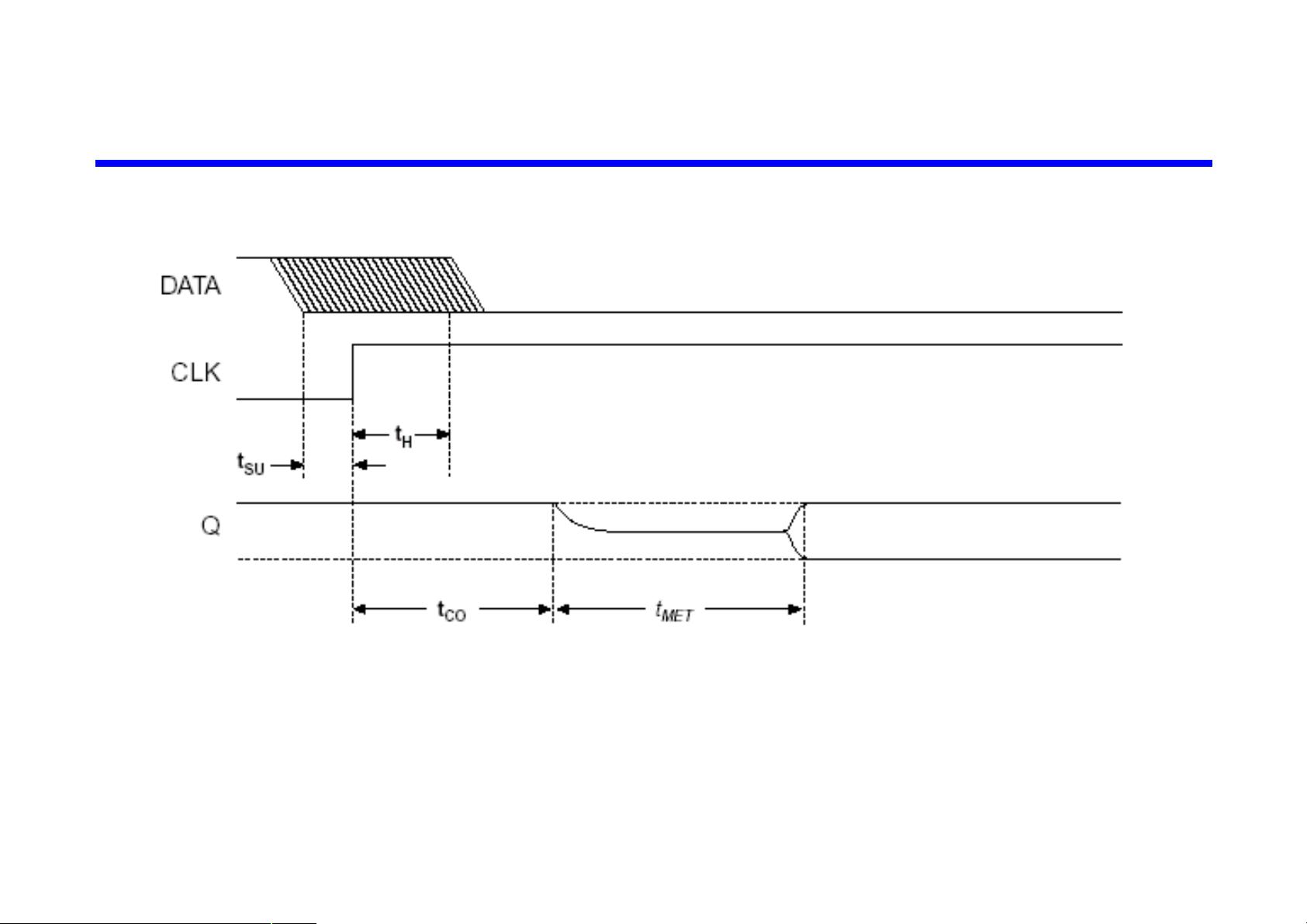

2. 目的:静态时序分析的主要目的是确保电路满足预定的时序约束,例如最大时钟周期或建立时间(setup time)和保持时间(hold time)要求。这有助于防止由于时序错误导致的数据丢失或错误。

3. 静态时序分析路径:分析通常包括查找从时钟到数据输入的最长路径(即最大延迟路径)。这些路径被称为“关键路径”,需要特别关注以优化电路性能。

4. 静态时序分析方法:包括路径分析、定时模型、时钟树综合(CTS)等。路径分析确定了每个路径的延迟,而定时模型则用于预测门延迟和互连线延迟。时钟树综合是为了确保时钟信号在整个芯片上的均匀分布,减少时序不确定性。

5. 静态时序分析工具:市场上有许多流行的工具,如Synopsys的PrimeTime,Mentor Graphics的SST Velocity,以及Innoveda的Blast89等。这些工具能够自动分析设计,提供详细的时序报告,并帮助工程师进行设计优化。

6. 时序分析报告及逻辑优化设计:报告通常包含路径延迟、时钟周期、时序违规等信息。逻辑优化设计旨在通过改进电路结构、减小门延迟或优化布线来缩短关键路径,以满足时序约束。

学习和理解静态时序分析对于任何从事ASIC设计或FPGA设计的工程师都至关重要,因为它直接影响到设计的性能和可靠性。通过掌握静态时序分析,工程师能够有效地优化设计,提高电路的运行速度,同时确保其满足严格的时序要求。

287 浏览量

270 浏览量

208 浏览量

379 浏览量

366 浏览量

274 浏览量

wan123459

- 粉丝: 0

- 资源: 3

最新资源

- 基于Cordova + Framework7 + React + Webpack构建混合App.zip

- CoronaGame_front

- 无线传感网络节点能耗模型.zip

- 蓝色扁平化商务工作汇报图表下载PPT模板

- ember-bootstrap-controls:一个Ember组件库,它使用Bootstrap4表单并输入样式和html

- PWABuilder-CLI:用于应用程序生成的Node.js工具

- XY轴点焊机_三菱伺服_

- 毕业设计,基于人脸识别的智能家居控制系统.zip

- rust-reference-book:中文版的Rust参考

- assignment-problem:匈牙利方法的分配问题

- 微立体建筑行业工作汇报图表大全PPT模板

- 电脑使用时间管理 ManicTime-4.3.rar

- firebase-firestore-lite:浏览器的轻量级云Firestore库

- bouquins:calibre 电子书管理器的 Web 前端

- MFC中修改Button控件字体、字体大小、背景色、背景图片

- Baymin是一个基于Android系统开发的可以用于语音聊天的智能机器人,它能够陪你聊天,帮你查天气,查路线、车票.zip