Vivado设计教程:从入门到实践

需积分: 9 82 浏览量

更新于2024-07-18

收藏 3.7MB PDF 举报

"这篇资源是关于Vivado的教程,主要来源于Xilinx的官方博客,适合需要学习Vivado设计流程的用户下载学习。教程涵盖了从基础到实践的设计步骤,适用于初学者和有一定经验的工程师。"

在Vivado教程中,我们将深入探讨如何使用Xilinx的Vivado软件来设计一个简单的数字电路,该电路是用Verilog HDL编写的。Vivado是一个综合性的硬件描述语言工具,它支持系统级设计、综合、仿真、实现和编程等全过程。本教程的目标是帮助你掌握Vivado的设计流程,以便能够针对基于Artix-7 FPGA的Nexys4开发板进行设计。

设计流程通常包括以下步骤:

1. 创建模型:这涉及到编写Verilog或VHDL代码来描述你的数字逻辑功能。

2. 创建用户约束文件:这些文件用于定义硬件设计的物理限制,如时钟速度、I/O引脚分配等。

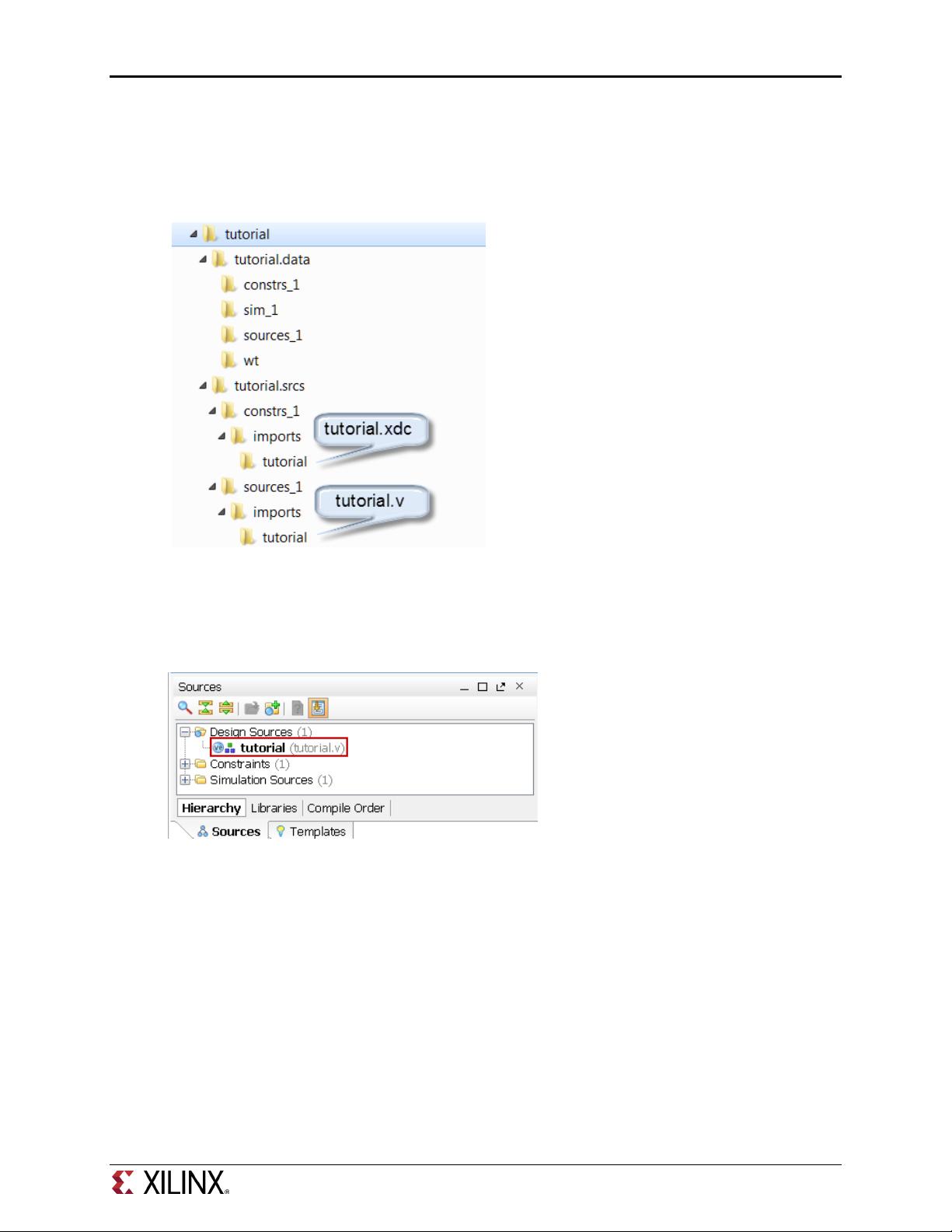

3. 创建Vivado项目:这是设计流程的起点,项目中会包含所有的源代码、约束文件和其他设计文件。

4. 导入模型:将编写好的Verilog代码导入到Vivado项目中。

5. 分配约束文件:将用户约束文件关联到相应的模块,确保设计满足硬件平台的要求。

6. 行为级仿真:在实际综合和实现之前,通过仿真验证设计的功能是否正确。

7. 合成设计:Vivado将高级语言描述转化为门级网表,优化逻辑结构以满足性能目标。

8. 实现设计:布局布线阶段,Vivado将逻辑网表映射到具体的FPGA逻辑单元和I/O资源上。

9. 生成比特流:完成布局布线后,生成可以下载到FPGA的配置文件(比特流)。

10. 硬件验证:通过下载比特流到Nexys4板子上,验证设计在真实硬件上的功能。

完成这个教程后,你将能够:

- 创建一个Vivado项目,引入HDL模型,并指定目标为Nexys4板上的特定FPGA设备。

- 使用提供的部分完成的设计模板,了解如何逐步完善和扩展你的设计。

- 理解并应用用户约束文件,以适应不同的硬件需求。

- 进行行为级仿真,确保设计在逻辑层面是正确的。

- 熟悉Vivado工具的各个阶段,从设计输入到最终的硬件验证。

本教程对于想要学习FPGA设计和Vivado工具的人来说是一份宝贵的资源,它将帮助你快速上手并实现自己的数字逻辑设计。无论是初次接触Vivado,还是希望提高现有技能,这个教程都能提供必要的指导和支持。

2013-05-20 上传

2020-08-13 上传

2020-03-06 上传

2023-04-23 上传

2018-01-19 上传

2023-04-23 上传

2024-08-27 上传

2022-08-20 上传

王瀑

- 粉丝: 0

- 资源: 1