PCIe总线技术与FPGA实现解析

版权申诉

103 浏览量

更新于2024-06-28

收藏 2.03MB DOCX 举报

"该文档详细介绍了PCI Express (PCIe) 总线的基础知识以及如何在FPGA设计中应用。文档从PCI总线的基本概念出发,深入解析PCIe总线技术,包括PCI总线的地址空间隔离、扩展性、速度提升等方面,并强调了PCIe在处理器系统中的角色和地位。此外,还探讨了PCIe与处理器、存储器、HOST主桥之间的交互关系,以及在FPGA设计中实现PCIe接口的关键点。"

PCI Express(PCIe)是一种高速串行计算机扩展总线标准,它是传统PCI总线的升级版,旨在提供更高的数据传输速率和更低的延迟。PCIe采用了点对点的连接方式,每个设备都有独立的数据通道,相比PCI总线的共享总线结构,能更有效地利用带宽。

1.1 PCI基础

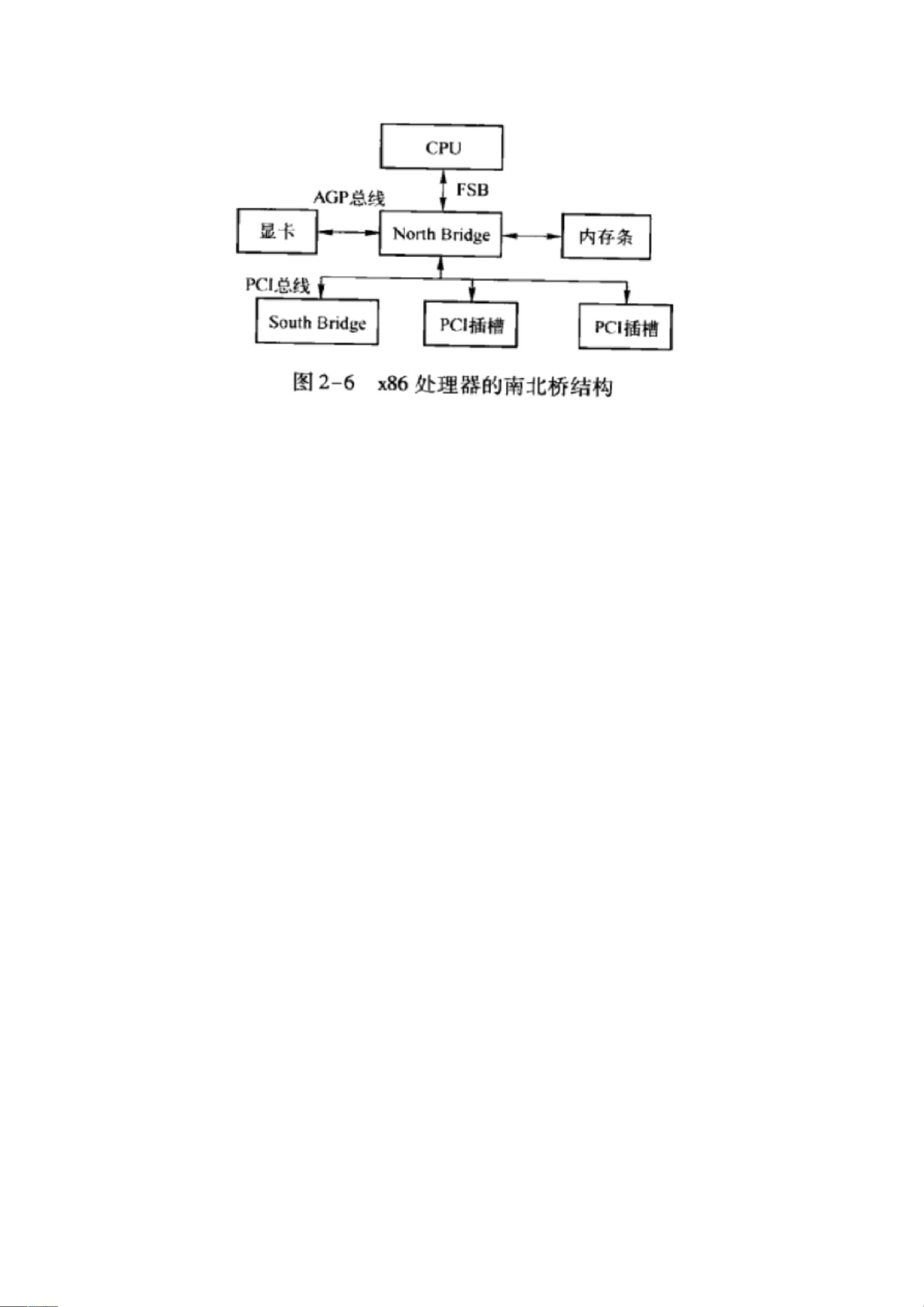

PCI总线最初设计用于连接处理器系统与外部设备,它的地址空间与处理器的存储器空间是分离的,通过HOST主桥进行访问和转换。HOST主桥扮演着关键角色,它不仅负责地址转换,还使得处理器可以访问PCI设备,同时PCI设备也能访问主存储器。在典型的处理器系统中,CPU域、DRAM域、存储器域和PCI总线域共同构建了一个完整的地址空间模型。

1.1.1 关键概念

- **PCI总线空间与处理器空间隔离**:PCI设备有独立的地址空间,通过HOST主桥与处理器和存储器地址空间相连,确保两者之间不直接交互。

- **可扩展性**:PCI总线设计允许系统扩展,支持多个设备同时连接,提供灵活的配置和性能提升空间。

- **存储器映射**:在x86系统中,外部设备空间与PCI总线地址空间重叠,处理器访问PCI设备时需经过HOST主桥进行地址转换。

1. PCIe基础

PCIe相比于PCI,采用串行传输,提供更高的数据带宽和更低的电气噪声。PCIe总线的每个通道(lane)可以独立传输数据,多个lane可以组成一个更宽的数据通道,例如PCIe x1、x4、x8、x16等。这种设计显著提高了数据传输速度。

在FPGA设计中,实现PCIe接口涉及到以下几个关键点:

- **协议栈**:理解PCIe的协议层次,包括物理层、数据链路层和网络层,以及相应的传输机制。

- **配置空间**:设置和管理PCIe设备的配置空间,用于设备识别和配置。

- **中断处理**:实现中断机制,确保PCIe设备与主机间的有效通信。

- **流控制和错误处理**:设计有效的流控机制以避免数据包丢失,并实现错误检测和恢复策略。

通过深入理解和掌握这些知识点,开发者能够成功地在FPGA设计中集成PCIe接口,从而实现高效、可靠的高速数据传输。无论是嵌入式系统、服务器平台还是其他高性能计算应用,PCIe都是连接处理器和外部设备的理想选择。

604 浏览量

201 浏览量

109 浏览量

2022-11-27 上传

756 浏览量

2022-07-02 上传

2022-10-30 上传

183 浏览量

2022-07-02 上传

不吃鸳鸯锅

- 粉丝: 8559

- 资源: 2万+

最新资源

- zakaz

- matlab实现DCT变换和量化

- snueue:Reddit 媒体播放器

- Digital-electronics-1-2021

- pids-mobile

- madplay.rar

- 使用 MATLAB 进行 3D 有限元分析:这些是“使用 MATLAB 进行 3D 有限元分析”网络研讨会中使用的 MATLAB 示例-matlab开发

- LOGA 5X 多语言多平台建站系统 v5.3.0 utf-8

- band-together

- 广州大学操作系统课程设计:优先级调度.zip

- zave7.github.io:主

- Python

- Yzncms内容管理系统 v1.0.0

- -deprecated-cmsimple:[已弃用] 使用机车 cms 或类似的 http

- 串口数据保存至TXT文件.rar

- threejs-camera-dolly:用于Threejs的相机多莉助手