FPGA片内DLL设计:快速锁定的延时锁相环优化

141 浏览量

更新于2024-08-28

收藏 387KB PDF 举报

"本文主要探讨了FPGA内部的延时锁相环(DLL)设计,尤其是关注于如何实现快速锁定的DLL技术。随着微电子技术的进步,FPGA的集成度和工作频率不断提升,但同时也带来了时钟延迟和偏斜的问题,影响系统性能。DLL作为数字时钟管理方案,因其设计简单、抗干扰性强、工艺可移植性好等优点,在FPGA中被广泛应用。文章介绍了DLL的基本结构和工作原理,并提出了新的OSDLL架构,以提高锁定速度,优化时钟性能。"

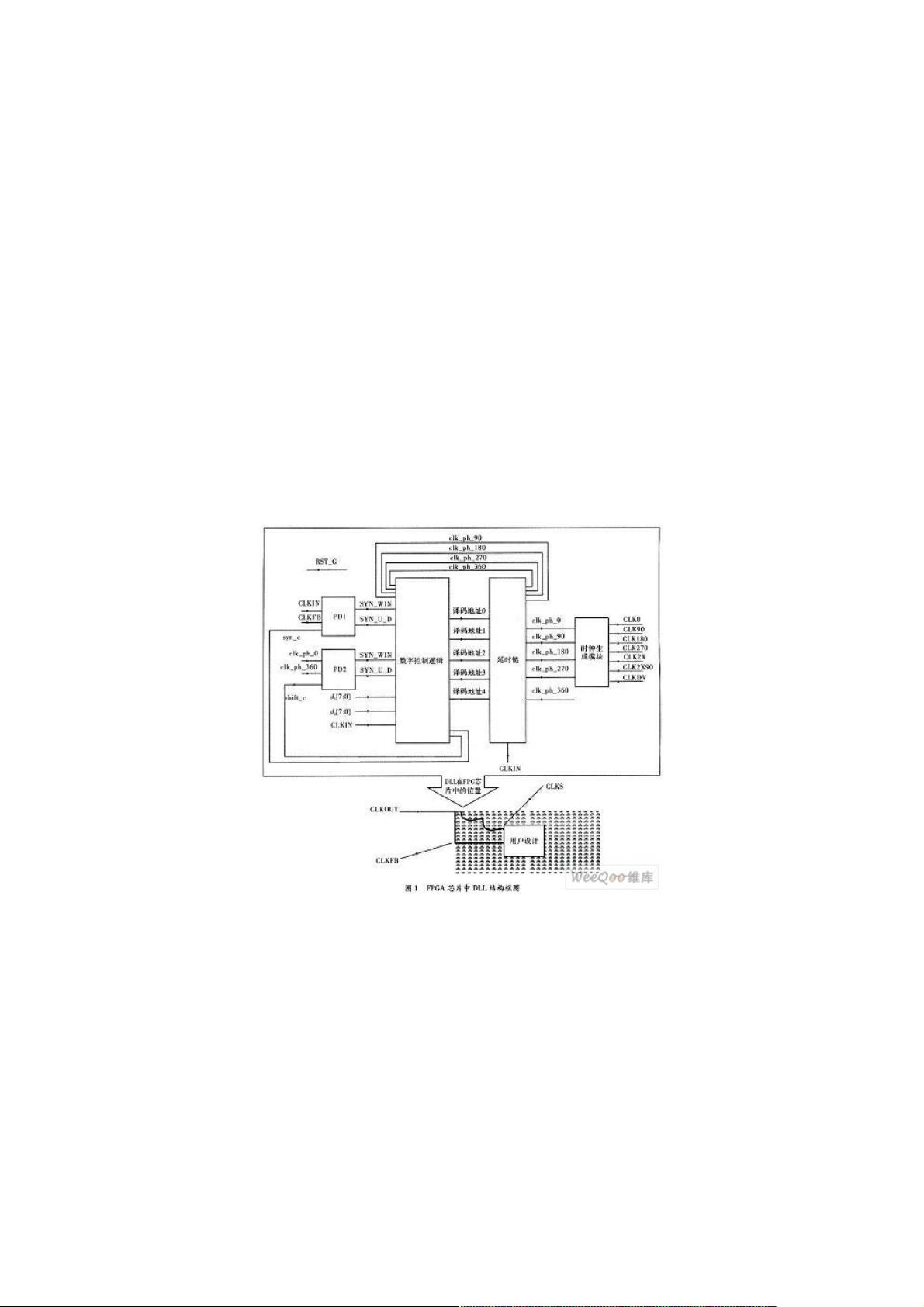

在FPGA设计中,时钟管理是至关重要的,因为它直接影响到系统的稳定性和性能。DLL(Delay-Locked Loop,延时锁相环)作为一种数字时钟管理技术,与传统的PLL(Phase-Locked Loop,相位锁相环)相比,尽管在时钟综合能力上稍逊一筹,但在数字系统中有着独特的优势。DLL主要由鉴相器、可调延时链、数字控制逻辑和时钟生成模块构成。当系统中存在时钟偏斜时,DLL通过调整输出时钟CLKOUT的相位,使其与反馈时钟CLKFB保持同步,从而消除时钟延迟,提升系统的时序性能。

DLL的工作流程如下:鉴相器比较输入时钟CLKIN和反馈时钟CLKFB的相位,根据相位差产生误差信号;这个误差信号通过数字控制逻辑调整可调延时链的延时,使CLKOUT的相位逐渐逼近CLKFB;当两者相位一致时,DLL达到锁定状态,此时输出时钟CLKOUT可以无偏斜地驱动FPGA内的时序逻辑,提供零传播延时。

传统DLL设计在锁定过程中可能需要较长的时间,这对于高性能系统来说是不可接受的。因此,文章提出了OSDLL(Optimized Synchronous DLL,优化同步DLL)架构,旨在缩短DLL的锁定时间。OSDLL可能采用了更先进的控制算法、更快的延时链调整机制或者改进的鉴相器设计,以实现更快的相位同步,同时保持系统稳定性。

FPGA中的DLL设计是解决高频率、高集成度环境下时钟管理问题的关键技术之一。通过理解DLL的工作原理和不断优化其设计,设计师能够更好地利用FPGA的资源,提高系统性能,实现快速且可靠的时钟同步。

2018-01-10 上传

2021-07-13 上传

点击了解资源详情

点击了解资源详情

2021-07-13 上传

2020-10-20 上传

2020-12-08 上传

2021-07-13 上传

点击了解资源详情

weixin_38655998

- 粉丝: 11

- 资源: 890

最新资源

- Aspose资源包:转PDF无水印学习工具

- Go语言控制台输入输出操作教程

- 红外遥控报警器原理及应用详解下载

- 控制卷筒纸侧面位置的先进装置技术解析

- 易语言加解密例程源码详解与实践

- SpringMVC客户管理系统:Hibernate与Bootstrap集成实践

- 深入理解JavaScript Set与WeakSet的使用

- 深入解析接收存储及发送装置的广播技术方法

- zyString模块1.0源码公开-易语言编程利器

- Android记分板UI设计:SimpleScoreboard的简洁与高效

- 量子网格列设置存储组件:开源解决方案

- 全面技术源码合集:CcVita Php Check v1.1

- 中军创易语言抢购软件:付款功能解析

- Python手动实现图像滤波教程

- MATLAB源代码实现基于DFT的量子传输分析

- 开源程序Hukoch.exe:简化食谱管理与导入功能