FPGA中的LVDS差分传输技术解析

"FPGA中LVDS差分高速传输的实现"

在数字电子技术领域,FPGA(Field-Programmable Gate Array,现场可编程门阵列)被广泛应用于高速数据传输和信号处理任务中。LVDS(Low Voltage Differential Signaling,低电压差分信号)作为一种高效、低功耗的高速数据传输技术,对于FPGA的设计和应用至关重要。LVDS通过在一对平衡传输线上以极小的电压差传输信号,从而显著提高了信号质量和传输速率,同时降低了电磁干扰(EMI)。

LVDS的主要优势在于其优秀的抗噪声能力。在理想情况下,LVDS信号的两个差分线路上,无论有无干扰,接收端都能够准确地恢复原始信号,因为噪声会同时作用于两条线上并相互抵消。这种特性使得LVDS在高噪声环境下的表现优于传统的单端信号传输。通常,LVDS支持的数据传输速率可超过155Mbps,甚至达到几百Mbps,适合高速通信需求。

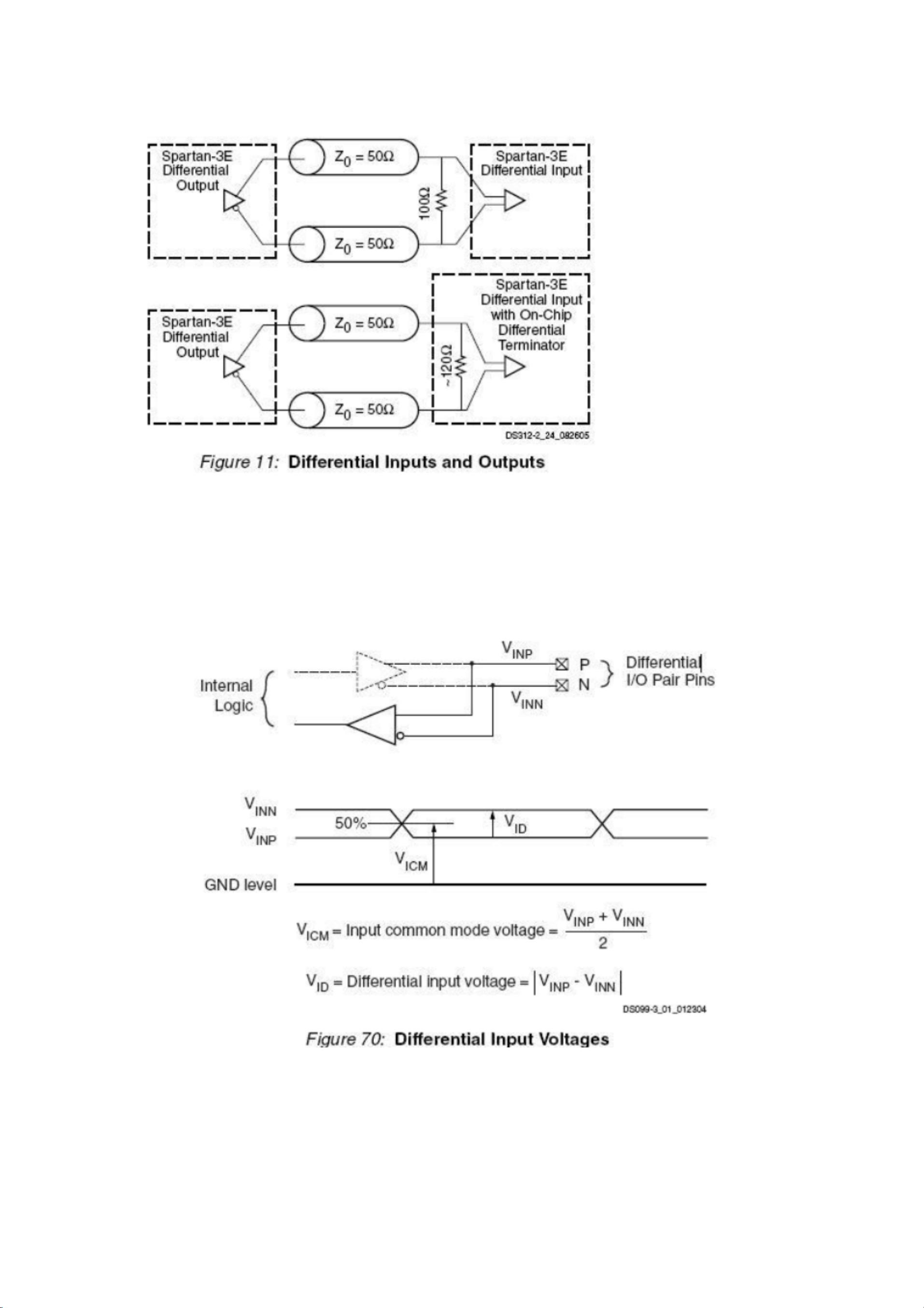

在Xilinx FPGA中,为了支持高速通讯,例如Spartan-3E系列,提供了多种差分接口标准,包括LVDS、BusLVDS、mini-LVDS、RSDS、Differential HSTL、Differential SSTL以及2.5V LVPECL输入等。这些接口的引入,极大地扩展了FPGA的应用范围,使其能够在各种高速数据传输应用场景中发挥作用。

对于FPGA的I/O管脚,它们通常采用特定的命名规则,以区分不同的接口类型。例如,LVDS接口的管脚可能会标记为“LVDS_XX”,其中“XX”可能是表示特定通道或功能的数字或字母组合。理解这些命名规则对于正确配置和使用FPGA的LVDS接口至关重要。

在实际应用中,设计者需要考虑诸多因素,包括信号完整性、电源管理、阻抗匹配以及电磁兼容性等,以确保LVDS在FPGA中的有效实施。例如,正确选择和匹配传输线的特性阻抗可以减少反射,提高信号质量;而合理的电源布局和滤波有助于降低噪声,保证系统的稳定运行。

LVDS在FPGA中的应用是现代高速数字系统设计中的关键环节,它不仅提供了高速数据传输的可能,还通过其优良的抗噪声特性,提升了系统的可靠性和效率。因此,深入理解和掌握LVDS技术,对于FPGA开发者来说至关重要,也是实现高效、高性能FPGA设计的基础。

2019-03-06 上传

2020-12-08 上传

2023-05-25 上传

2021-10-08 上传

2021-07-13 上传

2021-07-13 上传

2021-07-13 上传

IFANR_TONG

- 粉丝: 6

- 资源: 2

最新资源

- Struts快速学习指南

- 新型 求真 有效 值芯片 AD536的应 用

- Convex Optimization book (pdf)

- Web Service配置示例(例子)

- ajax方式载入外部页面数据的层打开效果.txt

- AJAX开发简略-简体中文教程

- 图书管理系统可行性分析

- STL_Tutorial_Reference.pdf

- GNU make中文手册

- How to Break MD5 and Other Hash Functions

- js精确定位HTML标签的TOP和LEFT值

- 高质量C编程指南 编程时我们经常忽视的地方

- QQ2440之初体验.pdf

- at89s52中文资料

- SAP人力资源管理功能概述

- S3C2440数据手册