VxWorks下基于FPGA内嵌MAC的千兆网UDP通信实现

需积分: 10 157 浏览量

更新于2024-09-11

1

收藏 411KB DOC 举报

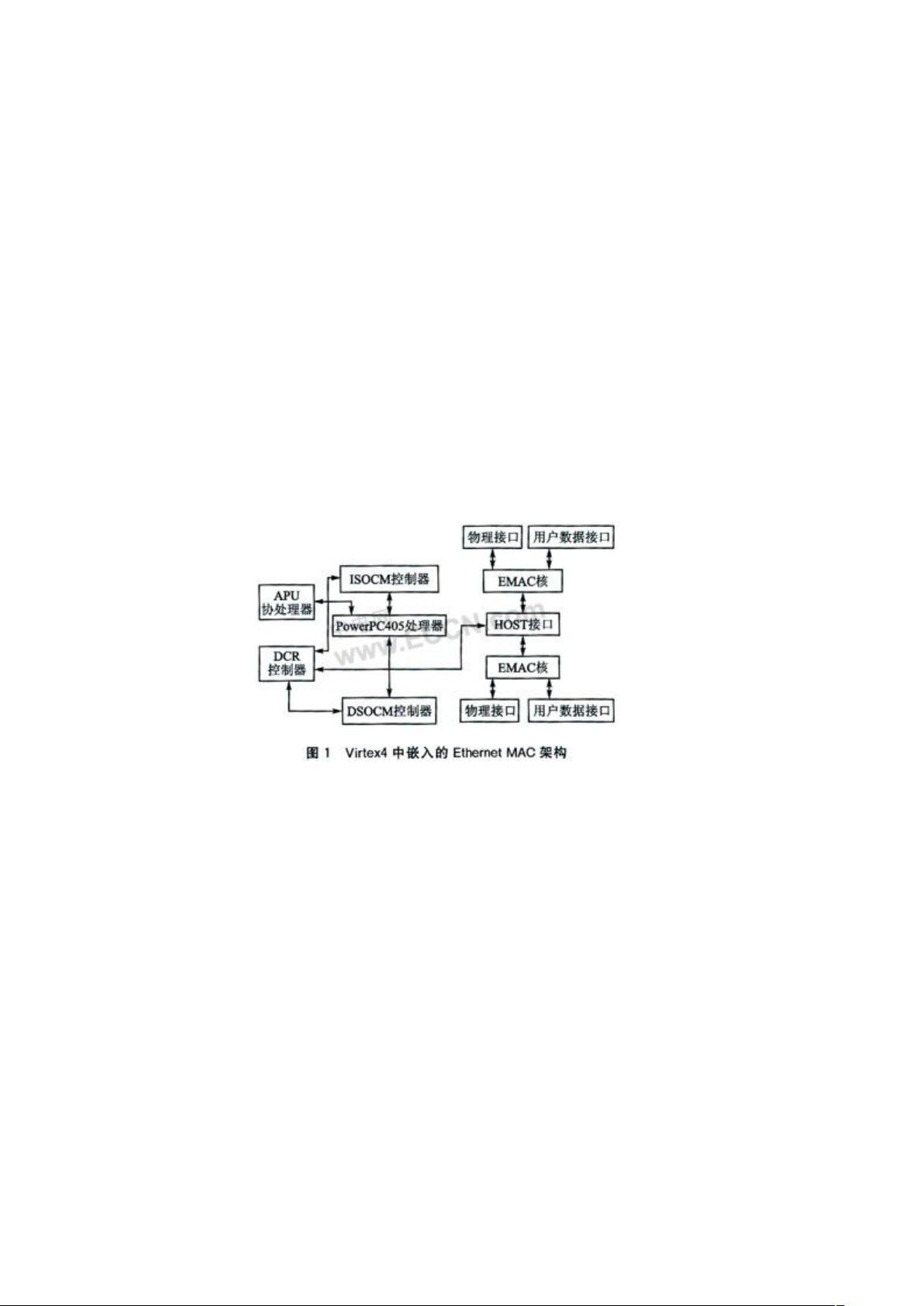

"本文主要介绍了如何在VxWorks操作系统下,利用片上PowerPC和Virtex4FX系列FPGA中的内嵌千兆EthernetMAC硬核实现UDP千兆网通信。设计涵盖了硬件架构、MAC内核的特点以及不同操作模式和接口类型。"

在现代的SoC(System on Chip)系统中,随着技术的进步,需求日益增长,百兆网通信已经无法满足高性能通信的需求。为了应对这一挑战,人们转向了千兆网通信。本文关注的是在VxWorks实时操作系统环境下,利用PowerPC处理器和Xilinx Virtex4FX系列FPGA的内置千兆通信硬核来构建UDP(User Datagram Protocol)网络通信。

Virtex4FX系列FPGA中的EMAC(Ethernet Media Access Controller)核心是一个关键组件,它提供了对半双工和全双工操作的支持,符合IEEE 802.3-2002标准,并且能够适应1Gbps、100Mbps和10Mbps的多种速率。此外,EMAC还支持MII(Media Independent Interface)、GMII(Gigabit Media Independent Interface)、RGMII(Reduced GMII)和SGMII(Serial GMII)等不同的通信接口,这些接口的灵活性使得适配不同的网络速度和硬件成为可能。

GMII是一个125MHz的并行接口,适合于1Gbps的传输速率,而RGMII则是一个25MHz的半字节并行接口,通过DDR(Double Data Rate)技术达到1Gbps的总带宽。在较低速模式下,MII接口则在100Mbps时工作在25MHz,10Mbps时工作在2.5MHz。

在VxWorks操作系统下,UDP作为一种无连接的传输协议,提供了一种快速且简单的方式来传输数据,尤其适用于不需要握手确认或者数据顺序保证的场景。在PowerPC处理器与FPGA的协同工作下,通过VxWorks的驱动程序接口,可以方便地实现UDP协议栈,从而实现在千兆网上的高效通信。

为了实现这一通信方案,需要进行以下步骤:

1. 配置FPGA中的EMAC核心,根据需求选择合适的接口模式和速率。

2. 编写或集成VxWorks的网络驱动程序,以支持EMAC硬件。

3. 实现UDP协议栈,处理数据的发送和接收。

4. 设计上层应用,通过VxWorks提供的API与UDP通信接口交互。

这个设计的优势在于,通过使用内嵌的MAC硬核,减少了设计复杂性,同时保持了高度的灵活性和性能。此外,由于EMAC核提供了网络管理特性,例如统计信息和流程控制,这对于系统的监控和故障排查非常有帮助。

片上PowerPC在VxWorks下结合Virtex4FX系列FPGA的千兆以太网硬核,为高带宽、低延迟的UDP通信提供了一个可靠且高效的解决方案,满足了现代高速通信的需求。

2020-10-24 上传

107 浏览量

117 浏览量

155 浏览量

118 浏览量

2022-09-24 上传

2011-09-18 上传

286 浏览量

liuxr08

- 粉丝: 0

- 资源: 1

最新资源

- 波特兰动画:受https:dribbble.comshots6136070-Los-Angeles启发

- in_CuZr_lammps_melt_

- 《狐狸爸爸鸭儿子》绘本故事PPT模板

- python代码自动办公 Excel_xlutils设置格式项目源码有详细注解,适合新手一看就懂.rar

- PHP实例开发源码-整形美容医院信息管理系统 v3.3.zip

- react-double-scrollbar:向内容添加顶部水平滚动条

- 清单:Website网站前端清单

- chrome-popup-bug-demo

- pytorch-faster-rcnn:pytorch1.0已更新。 支持CPU测试和演示。 (使用detectron2,这是一个杰作)

- linux 目录结构及作用说明.rar

- Snow Drift-crx插件

- react-twilio-video-post

- 基于随机游走算法的气体扩散matlab仿真模拟+仿真操作录像

- HighFrequencyDataOfFTSE100:英国脱欧公投日富时100高频数据分析

- python代码自动办公 用Python批量重命名文件项目源码有详细注解,适合新手一看就懂.rar

- ActiveMQ.zip