Verilog基础概述:运算符与模块结构详解

需积分: 0 22 浏览量

更新于2024-08-05

1

收藏 1.04MB PDF 举报

Verilog HDL,全称为Verilog Hardware Description Language,是一种广泛应用于电子设计自动化(EDA)领域的硬件描述语言。它提供了一种从高层次的算法描述(行为级)到低层次的电路实现(结构级)的建模工具,适用于数字系统的设计和验证。

1. **运算符和比较**:

- 加法、减法、乘法、除法和取模运算符用于处理数值计算,分别是 `+`、 `-`、 `*`、 `/` 和 `%`。

- 比较运算符包括 `<` (小于)、 `>` (大于)、 `<=` (小于等于) 和 `>=` (大于等于),用于逻辑判断和条件控制。

2. **模块和端口**:

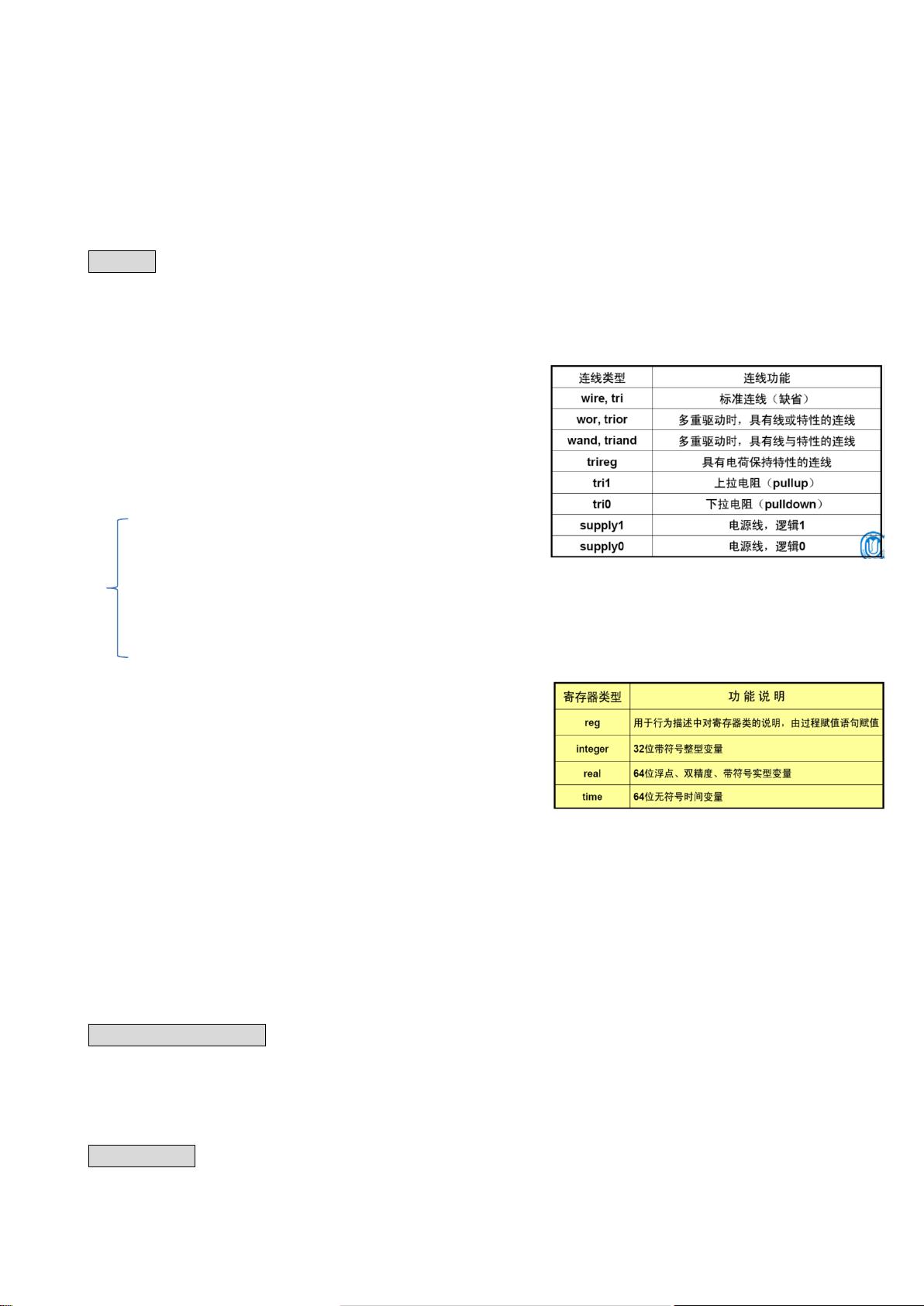

- Verilog中的模块是设计的基本构建单元,定义从`module`开始,到`endmodule`结束。模块定义包含模块名、端口声明(input、output、inout类型)和数据类型声明(wire或reg)。

- 模块的端口是外部接口,代表硬件电路的引脚,它们连接外部设备或信号源。

3. **描述层次**:

- 行为描述关注算法和功能的实现,通过模块描述逻辑流程。结构描述则关注电路的物理连接,如门级和开关级设计。

- VHDL倾向于系统级描述,适合系统架构设计,而Verilog更适合电路级细节,适合硬件工程师。

4. **测试与仿真**:

- 测试是在Verilog设计中不可或缺的部分,通过TestBench(测试台)来输入信号并检查DUT(待测单元)的输出。TestBench包含了激励信号源和输出结果的检测部分。

- 过程语句如`Initial`用于一次性初始化行为,`Always`则构成一个无限循环,通常配合触发条件进行连续执行。

5. **基本词法**:

- Verilog语句由空白符组成,包括空格、制表符、换行符和换页符,它们用于组织代码结构。

学习Verilog HDL需要掌握基本的运算符和比较,模块设计原则,以及不同层次的描述方法。同时,理解如何编写测试和初始化过程,以及熟悉Verilog的基本词法规则,对于有效进行硬件设计和验证至关重要。通过实践项目和熟悉相关工具,可以提升在实际工程中的应用能力。

2022-06-20 上传

2021-04-25 上传

2012-11-04 上传

点击了解资源详情

2021-06-17 上传

2010-03-03 上传

2023-02-27 上传

白羊带你成长

- 粉丝: 30

- 资源: 328

最新资源

- 人工智能原理实验.zip

- VCPP-Matlab.m.rar_matlab例程_Visual_C++_

- Thumbak-开源

- fso:快速[链接]缩短器

- try-haxe:允许在线测试Haxe的小型Webapp

- WordPress,经过Git验证。 每15分钟通过SVN同步一次,包括分支和标签! 该存储库只是WordPress Subversion存储库的镜像。 请不要发送请求请求。 而是将补丁提交到https://core.trac.wordpress.org/。-PHP开发

- thulcd.rar_微处理器开发_C++_Builder_

- spark-twitter-sentiment-analysis:具有Spark结构化流的Twitter主题的情感分析

- 人工智能检测恶意URL.zip

- Flaunt-crx插件

- mqtest:MQtest是一个简单的工具,可帮助您识别设备对哪些媒体查询做出响应

- Boxobox:与配套应用程序连接的Arduino机器人项目

- 人工智能直通车第二期 - 第八周作业.zip

- unholy_mess:项目计划软件

- 有效的外壳程序第2部分:成为剪贴板体操运动员

- ejercicios_tema3.zip_Perl_