EDA技术复习关键点:ASIC, FPGA, EDA工具与设计流程

下载需积分: 35 | DOC格式 | 6.02MB |

更新于2024-07-15

| 86 浏览量 | 举报

"这是一份关于EDA技术的期末复习资料,主要针对大学生的学习需求,涵盖了EDA技术的基础概念、设计方法和重要工具。"

EDA技术,全称为Electronic Design Automation,即电子设计自动化,是现代电子系统设计的核心工具。它包括了一系列用于设计、验证、模拟、综合、布局布线以及测试的软件工具,使得复杂的集成电路设计变得更加高效和便捷。在本复习资料中,重点强调了以下几个关键知识点:

1. 基本概念:

- ASIC(Application Specific Integrated Circuit):专用集成电路,为特定应用定制的芯片。

- IP(Intellectual Property):知识产权,指在电子设计中可重用的电路模块。

- HDL(Hardware Description Language):硬件描述语言,如Verilog和VHDL,用于描述电子系统的功能和行为。

- PLD(Programmable Logic Device):可编程逻辑器件,如PAL和GAL。

- CPLD(Complex Programmable Logic Device):复杂可编程逻辑器件,比PLD更复杂,具有更多可编程逻辑资源。

- FPGA(Field-Programmable Gate Array):现场可编程门阵列,高度灵活,可应用于各种应用场景。

- SOC(SYSTEM ON A CHIP):片上系统,将多个功能集成在一个芯片上。

- SOPC(SYSTEM ON A PROGRAMMABLE CHIP):可编程器件上的系统,利用FPGA实现SOC设计。

- PCB(Printed Circuit Board):印制电路板,承载和连接电子元件的平台。

- RTL(Register Transfer Level):寄存器传输级,描述数字电路中数据在寄存器间的转移。

- LPM(Library of Parameterized Modules):参数可设置模块库,提供可配置的电路模块。

- FSM(Finite State Machine):有限状态机,用于描述和实现数字系统的控制逻辑。

- ISP(In-system programmable):在系统可编程,允许设备在系统运行时进行编程。

- UDP(User Defined Primitives):用户自定义原语,允许设计者创建自己的基本逻辑单元。

2. 综合(Synthesis):

- 综合是将高级设计语言(如Verilog或VHDL)转换为门级网表的过程,以便于后续的布局布线。

- 综合过程中涉及6层模型:系统级、算法级、RTL级、门级、电路级和版图级。

- 综合包括转换、映射和优化三个步骤,可以采用图形界面或命令行方式执行。

3. 设计方法:

- 自顶向下设计:从系统级开始,逐步细化到组件级别,更利于仿真和验证,是现代Verilog设计的主流方法。

- 自底向上设计:从单个组件开始,逐渐构建到整个系统,适用于已有的模块化设计。

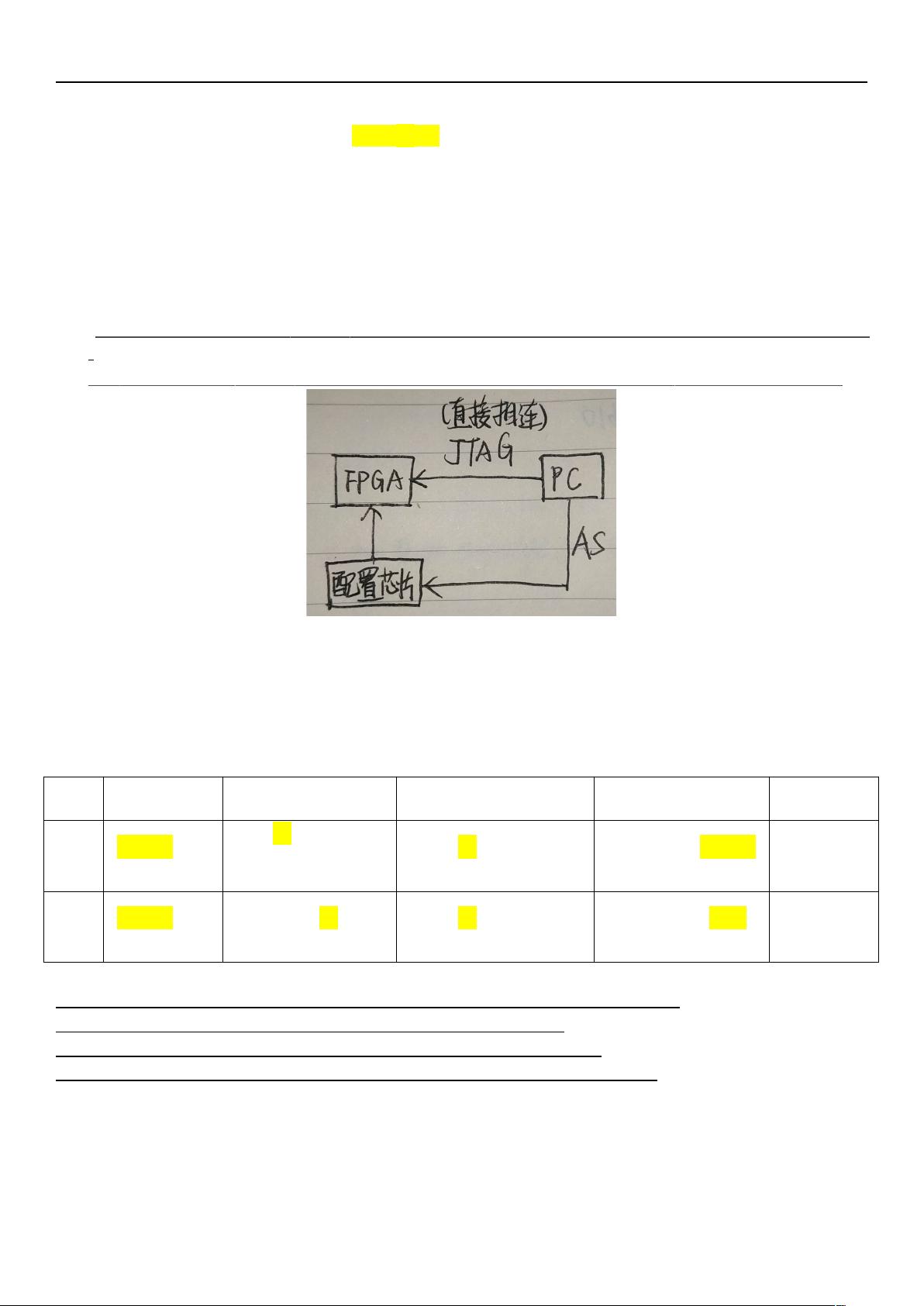

复习资料还提到了JTAG(Joint Test Action Group)联合测试行为组织,它是一种标准接口,用于芯片的边界扫描测试,以及GAL(Generic Array Logic)通用阵列逻辑和LUT(Look-Up Table)查找表等概念。这些工具和技术在现代电子设计中扮演着重要角色,是理解和掌握EDA技术的基础。通过学习和掌握这些知识点,学生可以更好地应对期末考试,并为未来在电子设计领域的实践打下坚实基础。

相关推荐

指尖侠

- 粉丝: 410

最新资源

- 渝海QQ号码吉凶查询工具PHP源码及多样化技术项目资源

- QT串口通信数据完整性解决方案

- DTcms V5.0旗舰版MSSQL源码深度升级与功能增强

- 深入探讨单片机的整机设计与多机通信技术

- VB实现鼠标自动连点技术指南

- DesignToken2Code:Sketch插件将设计标记自动转换为SCSS代码

- 探索Android最佳实践:MVP、RxJava与热修复

- 微软日本发布Win7萌系主题包:5位萌少女主题全体验

- Scratch3.0编程启蒙源代码包:少儿教育与创造力培养

- 实现汉字简繁转换的JavaScript代码教程

- Debian环境下Alacritty终端模拟器的软件包发布

- Mybatis自动生成代码工具:快速实现代码生成

- 基于ASP.NET和SQL的选课系统开发与实现

- 全面掌握Swift开发的权威指南解析

- Java实现的HTTP代理测试工具ProxyTester

- 6至10岁儿童Scratch3.0积木编程源代码下载