Zynq-7000 SoC PCB设计指南:UG933修订历史与布局要点

需积分: 17 171 浏览量

更新于2024-07-09

收藏 2.8MB PDF 举报

本资源为《Zynq-7000 SoC PCB设计指南》(UG933, v1.13.1),发布日期为2019年3月14日,由Xilinx公司提供。该文档是针对Xilinx Zynq-7000系统级芯片(SoC)的详细PCB设计手册,旨在帮助设计师在实际项目中优化电路板布局和元器件选择,确保系统性能和稳定性。

Zynq-7000是一款集成处理系统,它集成了ARM处理器和可编程逻辑(FPGA)于一个芯片,因此对PCB设计的要求较高,需要考虑处理器和FPGA之间的接口、电源管理、时钟信号以及信号完整性等因素。文档包含了丰富的技术细节,如:

1. **修订历史**:记录了文档从初始版本1.0到v1.13.1的更新历程,涉及格式修正、内容增补和错误更正,显示了Xilinx持续关注文档的完善性和准确性。

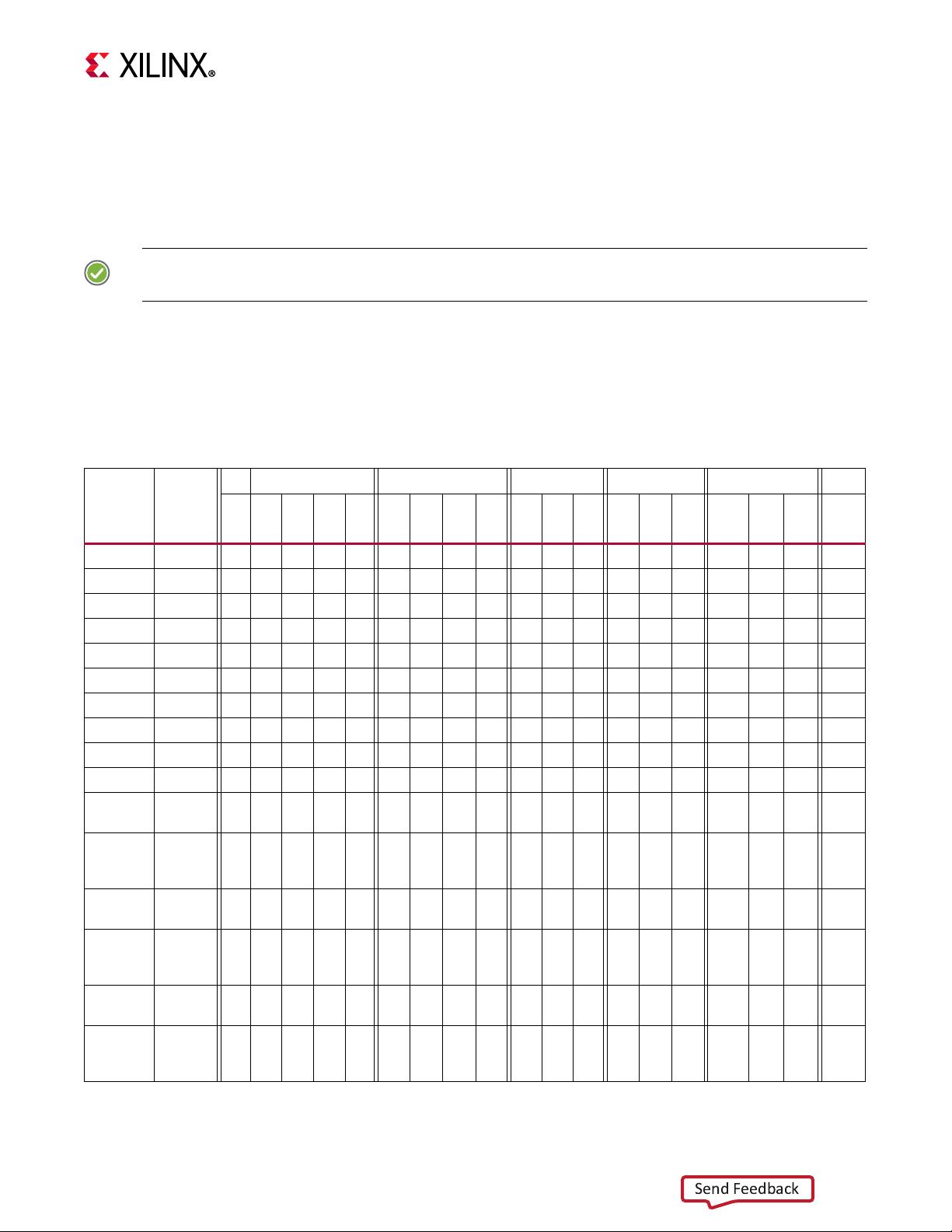

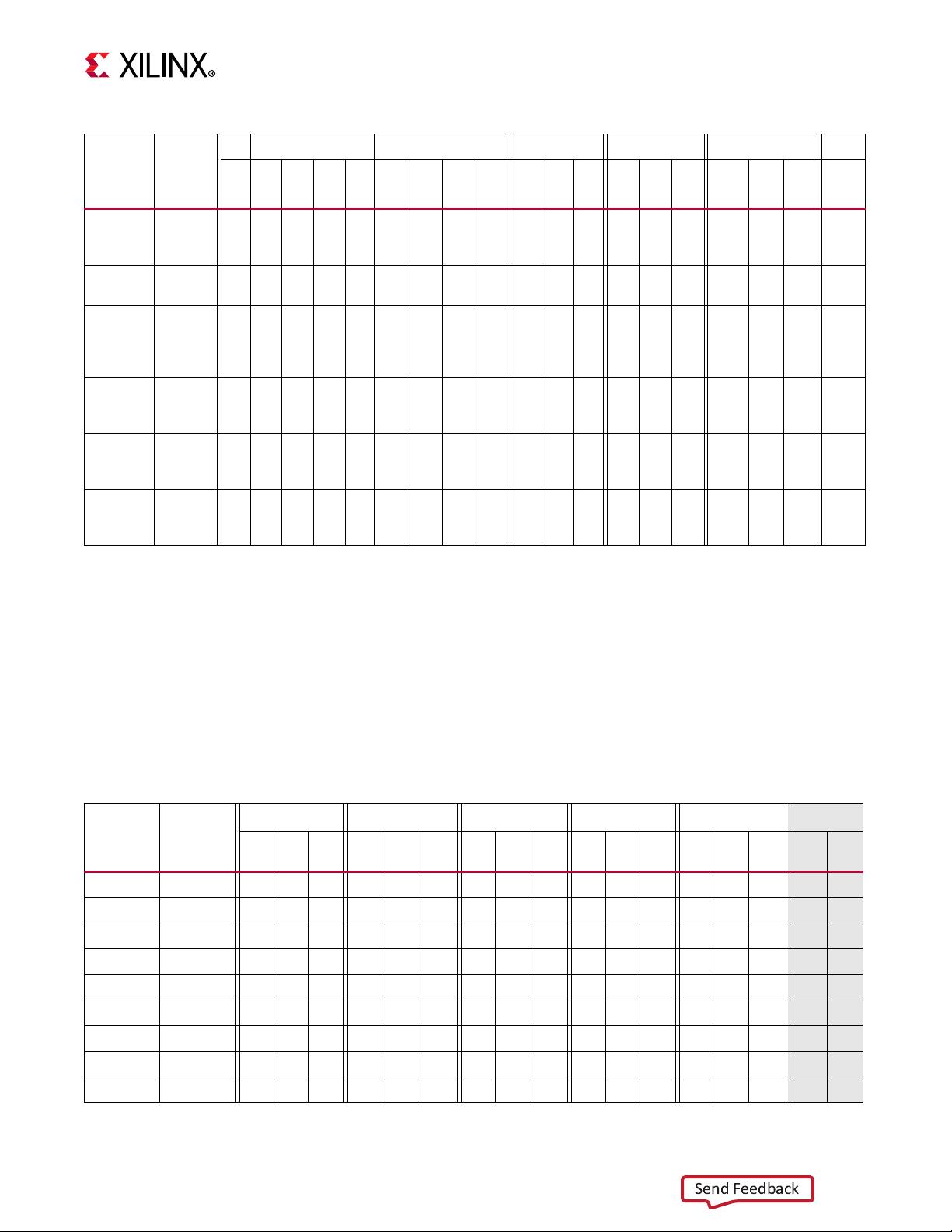

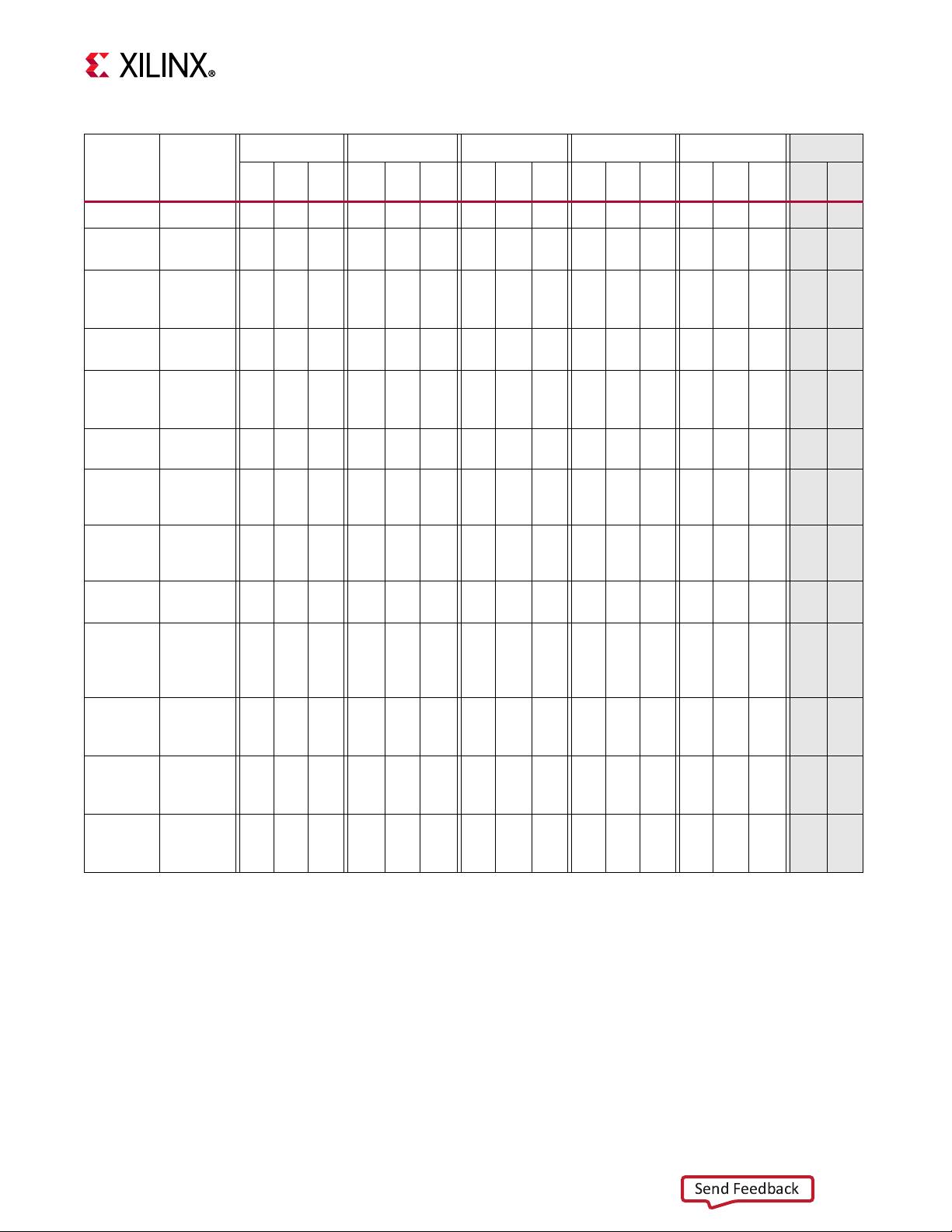

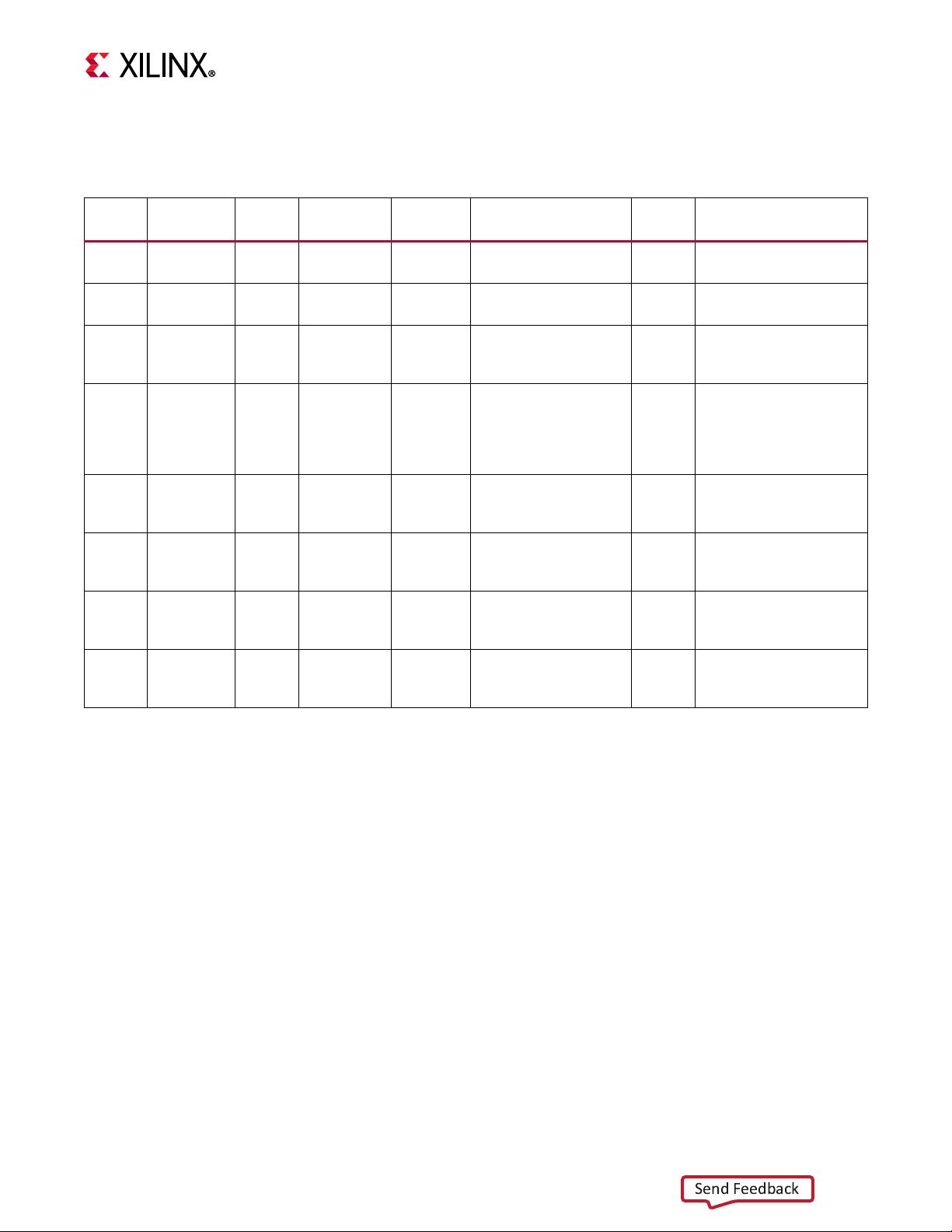

2. **表3-1和3-2**:可能包含不同Zynq-7000设备或封装的规格信息,这些数据对于选择正确的组件至关重要。此外,表3-3中添加了680微法(FuF)电容规格,强调了电源滤波和信号质量的重要性。

3. **VCCPAUX和VCCPLL**:指南详细介绍了PS辅助逻辑供电(VCCPAUX)和PS PLL供电(VCCPLL)的相关参数,包括推荐的电压范围、连接方式变化(从下拉电阻改为上拉电阻),以及注意事项,这涉及到电源管理的精确控制。

4. **DDR供电电压**:文档对PS_DDR_VREF0和PS_DDR_VREF1引脚的DDR参考电压进行了修改,这是确保内存工作稳定的关键,可能涉及电压设置的建议和注意事项。

5. **信号完整性**:通过图示,如Figure5-3和5-5,展示了MIO(主要输入/输出)接口的Cke引脚的更改,可能涉及信号传输速度和噪声抑制的设计策略。

此文档为Zynq-7000 SoC的PCB设计者提供了详尽的指导,涵盖了元器件选择、电源管理、接口规范以及信号完整性等关键设计要素,是进行高效和高质量PCB设计的重要参考资料。设计人员在实际项目中应遵循其中的规则和建议,以实现系统的最佳性能和可靠性。

283 浏览量

275 浏览量

378 浏览量

2254 浏览量

243 浏览量

1133 浏览量

104 浏览量

398 浏览量

697 浏览量

weixin_41370347

- 粉丝: 0

最新资源

- Actionscript3.0动画基础教程:从概念到实践

- 有限样本下的统计学习与核方法:支持向量机简介

- 中国联通Vasp接口技术详解:ParlayX与第三方协作指南

- Oracle9i查询优化深度解析:提升性能的关键技术

- 中国联通SP接口规范v1.3详解:业务订购与取消

- Nutch学习教程:从入门到精通

- C#实用教程:掌握正则表达式

- CMM1.1:提升软件开发能力的关键模型

- MyEclipse快捷键大全:提升编程效率的秘籍

- 使用load()或reload()加载数据库连接脚本

- CSS初学者指南:掌握基本知识与技巧

- C++设计新思维:泛型编程与设计模式应用

- 提升网站速度与美感:高手实战 Yahoo! 绩效优化策略

- PCIExpress深度解析:下一代高速I/O接口

- SQL Server 2005 Reporting Services 中文教程:创建报表服务器项目

- R语言数据导入导出指南