"MIPS单周期CPU设计及Verilog硬件描述语言实现"

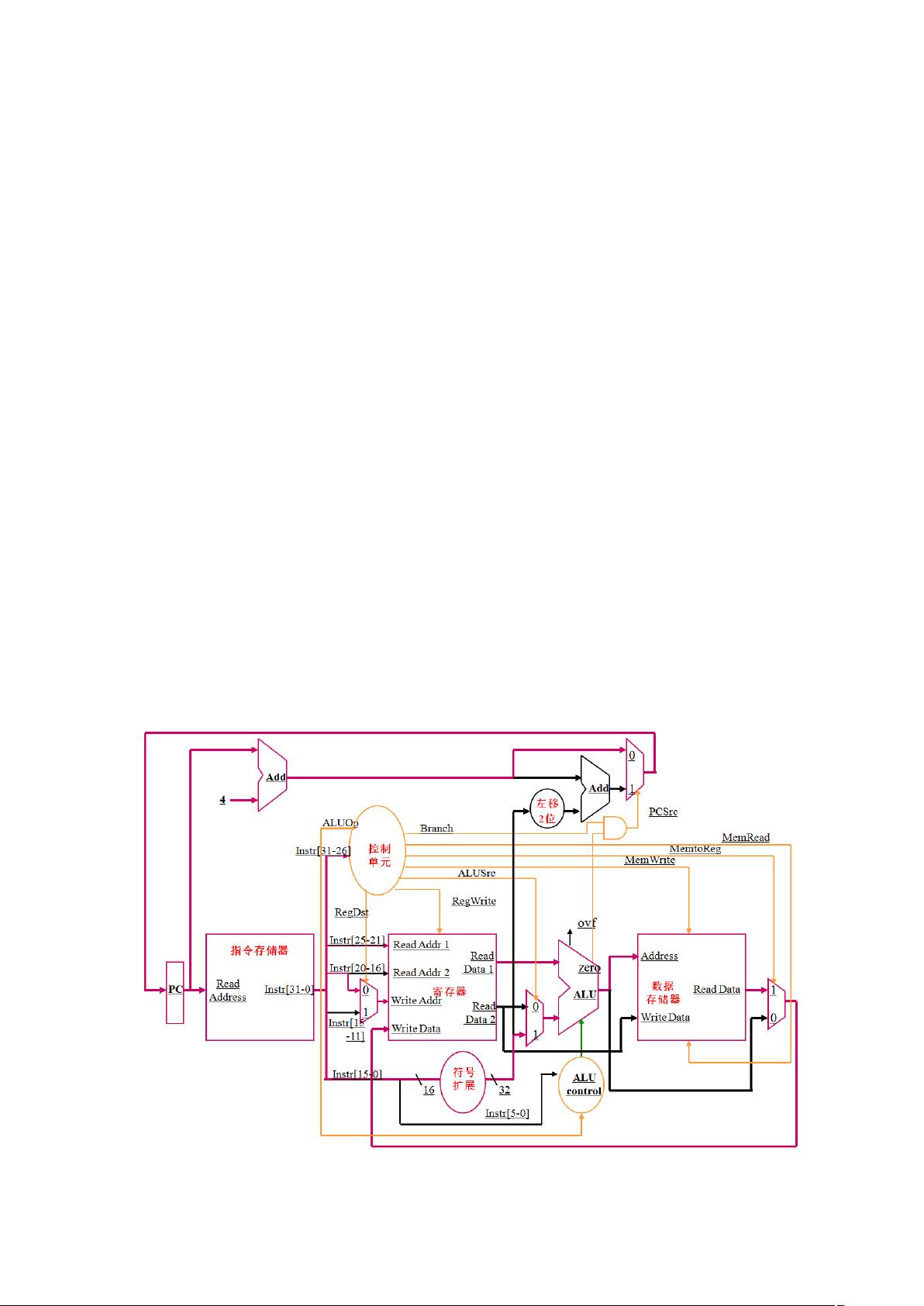

本课程设计报告旨在介绍通过硬件描述语言(Verilog)设计32位MIPS单周期CPU,并使用模拟软件Modelsim对汇编程序进行仿真测试的全过程。本次设计涉及到多个模块的设计,包括程序计数器模块(PcUnit)、指令存储器模块(IM)、寄存器模块(GPR)、数据扩展模块(Extender)、运算器模块(Alu)、数据存储器模块(DMem)、控制器模块(Ctrl)以及整机连接模块(Mips)等。通过对这些模块的设计和连接,完成了对指令集{ lw,sw,addu,subu, ori, sll, srl, beq,bne }的支持,并成功对汇编程序进行了仿真调试。

本次课程设计的主要内容包括对硬件描述语言(Verilog)和仿真软件Modelsim的熟悉,通过设计各种模块的方式来实现对MIPS单周期CPU的构建。首先,我们设计了程序计数器模块(PcUnit),用于存储当前指令的地址,并且能够根据控制信号实现地址的更新。其次,指令存储器模块(IM)被设计出来,用于存储所有的指令,便于根据地址进行读取。接下来,寄存器模块(GPR)的设计使得CPU能够进行寄存器的读写操作。数据扩展模块(Extender)则用于实现数据的零扩展和符号扩展。运算器模块(Alu)实现了常见的算术逻辑运算,以及移位运算等功能。数据存储器模块(DMem)则用于存储数据,并且支持对数据的读写操作。控制器模块(Ctrl)的设计使得CPU能够根据不同的指令进行相应的控制操作。最后,整机连接模块(Mips)将上述各个模块进行连接,构建了完整的32位MIPS单周期CPU。

在所有模块的设计完成之后,我们使用仿真软件Modelsim对编写的汇编程序进行了测试。通过对模拟运行的过程进行观察和调试,最终得出了期望的运行结果。从整个课程设计的过程来看,我们深刻理解了MIPS单周期CPU的设计原理和实现方法,同时也掌握了硬件描述语言(Verilog)的使用技巧,并且对仿真软件Modelsim有了更加深入的了解。通过本次课程设计,我们对计算机组成原理有了更加系统和全面的认识,并且进一步锻炼了自己的动手能力和问题解决能力。

在完成本次课程设计之后,我们对计算机硬件的设计有了更加深入的了解,能够更加熟练地使用硬件描述语言(Verilog)进行设计,以及运用仿真软件Modelsim进行验证和调试。这对于我们今后的学习和工作都有着重要的意义。同时,本次课程设计也对我们的团队合作能力和解决问题的能力提出了挑战,最终我们通过共同的努力克服了困难,顺利完成了任务。我们相信,通过本次课程设计的学习和实践,我们的能力得到了进一步的提升,为今后的学习和工作打下了坚实的基础。

169 浏览量

2024-06-06 上传

2023-06-13 上传

2023-05-14 上传

2024-05-21 上传

2023-07-09 上传

2023-06-28 上传

2023-06-28 上传

lfn.

- 粉丝: 3

- 资源: 15

最新资源

- Aspose资源包:转PDF无水印学习工具

- Go语言控制台输入输出操作教程

- 红外遥控报警器原理及应用详解下载

- 控制卷筒纸侧面位置的先进装置技术解析

- 易语言加解密例程源码详解与实践

- SpringMVC客户管理系统:Hibernate与Bootstrap集成实践

- 深入理解JavaScript Set与WeakSet的使用

- 深入解析接收存储及发送装置的广播技术方法

- zyString模块1.0源码公开-易语言编程利器

- Android记分板UI设计:SimpleScoreboard的简洁与高效

- 量子网格列设置存储组件:开源解决方案

- 全面技术源码合集:CcVita Php Check v1.1

- 中军创易语言抢购软件:付款功能解析

- Python手动实现图像滤波教程

- MATLAB源代码实现基于DFT的量子传输分析

- 开源程序Hukoch.exe:简化食谱管理与导入功能