FPGA时钟资源解析:DCM、PLL、PMCD与MMCM的应用

下载需积分: 12 | PDF格式 | 419KB |

更新于2024-09-05

| 57 浏览量 | 举报

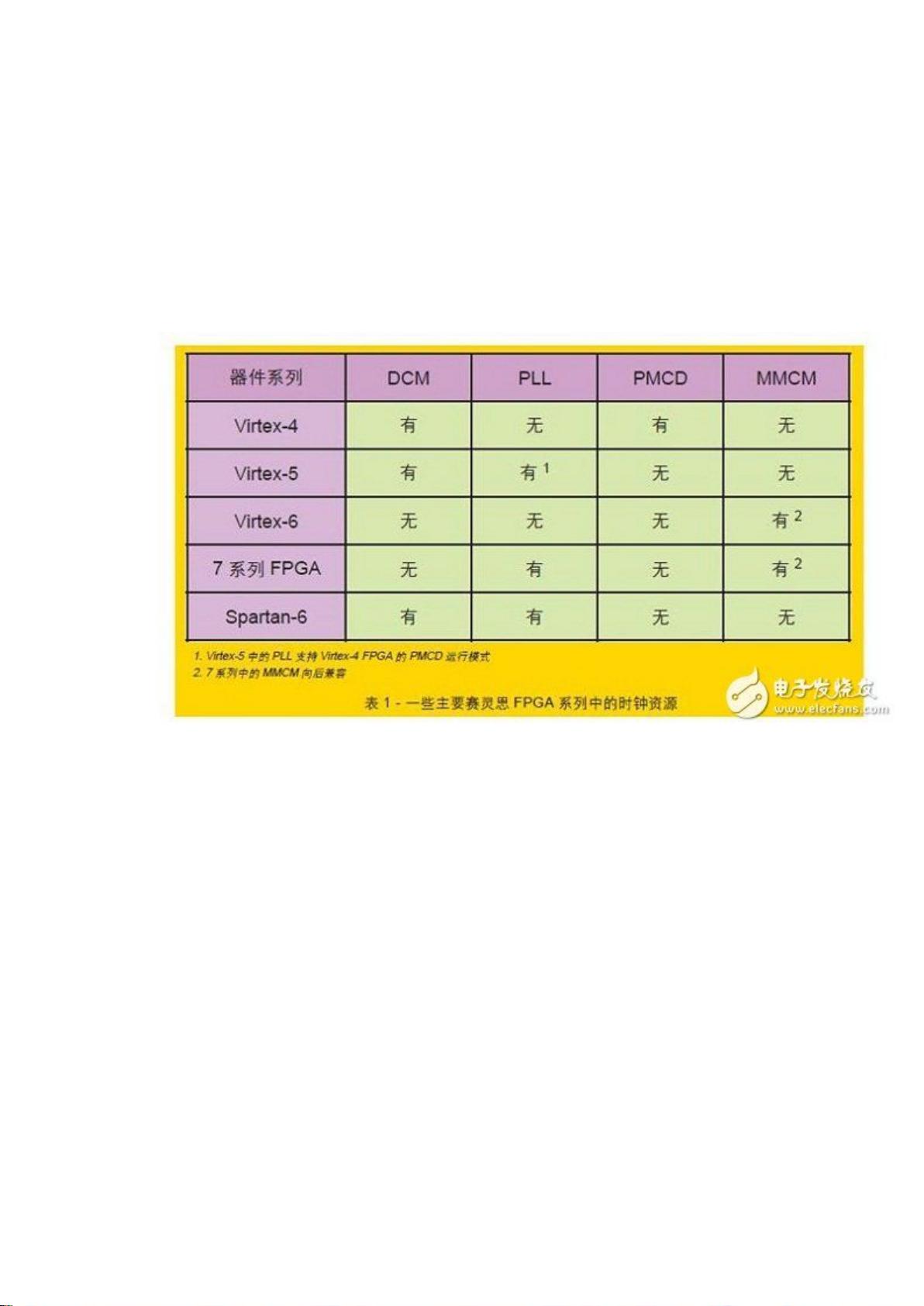

"该文档主要介绍了如何正确使用FPGA中的时钟资源,包括DCM(数字时钟管理器)、PLL(锁相环)、PMCD(相位匹配时钟分频器)和MMCM(混合模式时钟管理器),强调了理解这些时钟资源在FPGA设计中的重要性。文档指出,不同类型的时钟资源适用于不同的应用场景,如DCM常用于DLL、DFS、DPS和时钟信号的处理,PMCD用于相位匹配的时钟分配,而PLL和MMCM则用于频率综合、抖动过滤等,并可以作为时钟信号的镜像或缓冲。文档还提到了考虑长期产品规划时,时钟策略的兼容性问题,并以Virtex-4 FPGA中的DCM为例,详细解释了其内部结构和工作原理。"

FPGA设计中,时钟资源的合理利用至关重要,因为它直接影响着系统的性能和稳定性。赛灵思FPGA提供了多种时钟管理模块,每种都有其特定的功能和适用范围。

1. DCM(数字时钟管理器):DCM主要用于时钟信号的整形和控制,它包含DLL(延迟锁相环),能消除输出时钟的歪斜,确保时钟信号的精确同步。DCM可以实现时钟的倍频和分频,同时支持数字相移,适用于需要灵活时钟调整的应用。

2. PLL(锁相环):PLL是一种广泛使用的时钟资源,它包含了压控振荡器(VCO),能够锁定到输入时钟,并提供频率合成、抖动过滤等功能。PLL能够生成与输入时钟不同频率的时钟,且可以作为时钟的镜像或缓冲。

3. PMCD(相位匹配时钟分频器):PMCD专门设计用于实现相位匹配的时钟分配,它可以确保多个时钟信号之间具有精确的相位关系,适合于需要严格时钟同步的应用场景。

4. MMCM(混合模式时钟管理器):MMCM与PLL类似,但也有一些增强特性,比如更精细的频率分辨率和更低的抖动。MMCM同样可以进行频率综合和时钟去歪斜,同时提供了更高级的时钟管理功能。

在选择和使用这些时钟资源时,设计者需要考虑应用需求、性能指标以及未来升级的兼容性。例如,如果设计需要精确的时钟相位匹配,那么PMCD可能是最佳选择;如果需要频率合成和抖动过滤,那么PLL或MMCM将更加合适。

此外,对于长期的产品规划,设计者应确保所选的时钟资源在不同FPGA系列间的兼容性,以便在未来升级或扩展设计时能平滑过渡。例如,Virtex-4 FPGA中的DCM有多种原语,理解这些原语的差异和特性可以帮助设计者做出更明智的选择。

理解并掌握FPGA中的时钟资源,如DCM、PLL、PMCD和MMCM,是实现高效、可靠FPGA设计的关键。每个模块都有其独特优势,根据具体应用需求来选择和配置时钟资源,可以优化系统性能,减少设计中的时钟相关问题。

相关推荐

weixin_38744153

- 粉丝: 348

最新资源

- VB通过Modbus协议控制三菱PLC通讯实操指南

- simfinapi:R语言中简化SimFin数据获取与分析的包

- LabVIEW温度控制上位机程序开发指南

- 西门子工业网络通信实例解析与CP243-1应用

- 清华紫光全能王V9.1软件深度体验与功能解析

- VB实现Access数据库数据同步操作指南

- VB实现MSChart绘制实时监控曲线

- VC6.0通过实例深入访问Excel文件技巧

- 自动机可视化工具:编程语言与正则表达式的图形化解释

- 赛义德·莫比尼:揭秘其开创性技术成果

- 微信小程序开发教程:如何实现模仿ofo共享单车应用

- TrueTable在Windows10 64位及CAD2007中的完美适配

- 图解Win7搭建IIS7+PHP+MySQL+phpMyAdmin教程

- C#与LabVIEW联合采集NI设备的电压电流信号并创建Excel文件

- LP1800-3最小系统官方资料压缩包

- Linksys WUSB54GG无线网卡驱动程序下载指南