FPGA实现二值图像边界检测算法

133 浏览量

更新于2024-09-03

1

收藏 283KB PDF 举报

本文主要介绍了如何在FPGA中实现二值图像的边界提取算法,通过3x3模板进行边缘检测,适用于单片机与FPGA交互的图像处理场景。

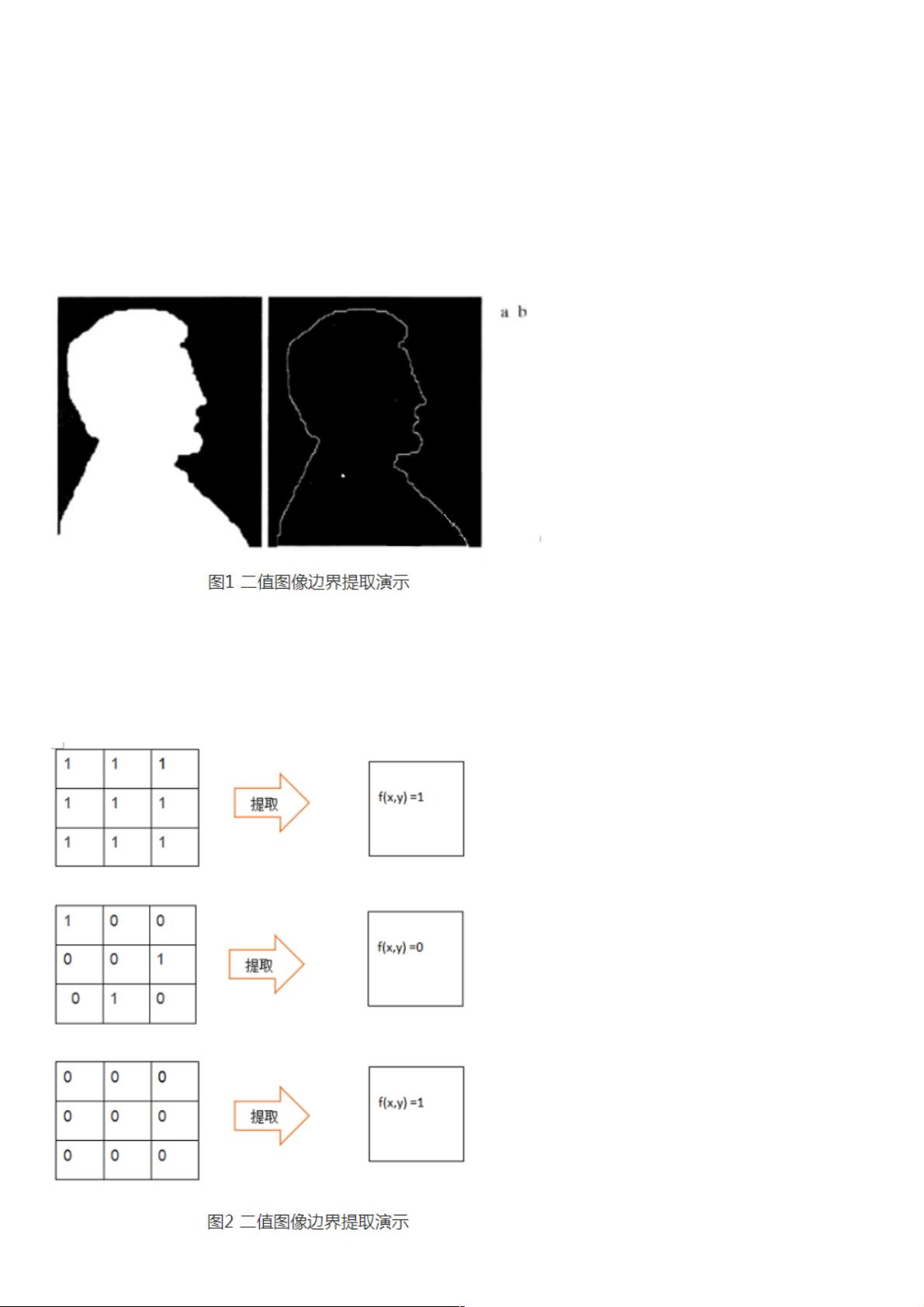

二值图像边界提取是图像处理中的基础操作,它用于识别图像中的物体轮廓。在图像处理领域,二值图像通常由黑白两种像素组成,其中白色像素代表物体,黑色像素代表背景。在给定的描述中,算法使用3x3的模板(也称为滤波器或结构元素)在图像上滑动,来检测像素的边界。

边界提取算法的工作原理如下:

1. 当3x3模板覆盖的9个像素全部为白色(即值为'1')时,认为该位置可能存在边界,因为所有相邻像素都是物体,输出也为'1'。

2. 同样,如果9个像素全为黑色('0'),则认为可能是边界,输出同样为'1'。这是因为在这种情况下,整个区域可能是背景,而边界可能位于模板的外围。

3. 在其他情况下,即模板中包含黑白混合的像素,输出设为'0',这表示这些位置不是边界。

在FPGA实现中,边界提取算法通常由硬件逻辑电路执行,以实现快速高效的处理。给定的FPGA源码模块`boundary_extraction`接收图像数据流,包括像素时钟`clk`、复位信号`rst_n`、水平同步信号`hs_in`、垂直同步信号`vs_in`以及16位的像素数据`data_in`。此外,还有输入数据有效标志`data_in_en`和相应的输出信号。模块会计算并输出处理后的图像数据到`data_out`,同时提供输出数据有效标志`data_out_en`,以便下游系统知道何时接收数据。

在FPGA内部,这个模块可能会采用并行处理的方式,对每个像素位置应用边界检测规则,生成新的二值图像。时钟信号`clk`控制着数据处理的同步,`rst_n`用于在系统启动时复位状态机,而`hs_in`和`vs_in`则用于同步图像帧的开始和结束。

实现时,可以采用查找表(LUT,Look-Up Table)或状态机来存储和执行边界检测规则。对于3x3模板,每个像素位置需要检查9个相邻像素,这意味着需要9次读取和比较操作。在FPGA中,这些操作可以并行化,从而显著提高处理速度。

FPGA实现的二值图像边界提取算法是一种高效的方法,尤其适用于实时或嵌入式系统,它能够快速地识别和输出图像的边缘信息,为后续的图像分析和处理步骤提供基础。

639 浏览量

点击了解资源详情

点击了解资源详情

2023-11-10 上传

153 浏览量

2023-03-13 上传

2010-08-16 上传

2022-10-25 上传

383 浏览量

weixin_38600460

- 粉丝: 5

最新资源

- 整合营销力量:CRX插件的推广与优化

- 电子科技大学概率论与数理统计优质课件分享

- jQuery手风琴图片滑动展示特效教程与下载

- 机器学习训练数据包:LineSVC与HOG结合手写识别

- VB中创建Code 39条形码的教程与代码示例

- 易语言实现的学校智能排课系统源码

- 深入解析Spring AOP编程技术及应用实例

- 鼠标颜色提取器:便捷获取颜色编码绿色版

- 多功能图标管理工具发布,操作简便效率高

- DaebWxHook:安全操作微信接口及关键文件介绍

- netMEDIA-crx插件:一站式招聘候选人来源

- 电子商务布局设计与响应式尺寸规范指南

- Git 2.25.1与TortoiseGit 2.2.0.0官方64位版安装指南

- 2017年张志君SpringBoot视频教程完整资料整理

- PowerCLI脚本库:自动化虚拟环境管理

- Adobe官方配色神器Kuler插件深度解析