清华大学微电子研究所集成电路设计实践Lab3:Verilog-A与OCEAN仿真

需积分: 10 100 浏览量

更新于2024-07-10

收藏 1.26MB PDF 举报

"eetop.cn_LAB3_669504162.pdf - 集成电路设计实践2013春实验室课程"

这篇文档是清华大学微电子研究所集成电路设计实践2013春季学期的实验三,主要涵盖了两个部分:Verilog-A模拟仿真和基于OCEAN的电路仿真。实验旨在让学生掌握混合信号系统设计的基础,特别是通过Verilog语言来描述数字和模拟组件。

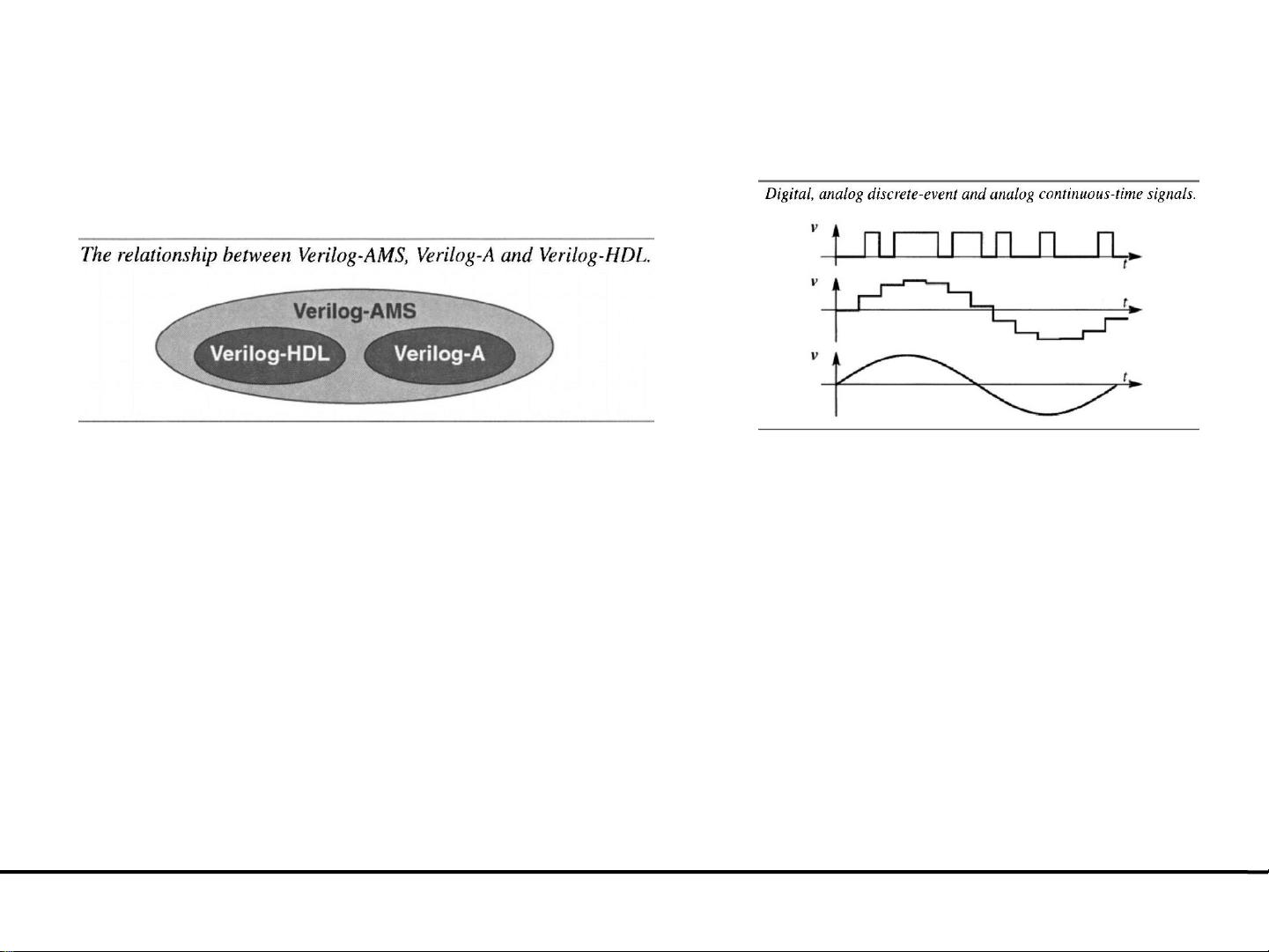

首先,文档提到了Verilog-A,这是一种用于模拟电路描述的语言扩展。在混合信号系统设计中,Verilog-A扮演了关键角色,因为它能够处理数字信号和模拟信号的处理部分。传统的Verilog-HDL主要用于描述数字逻辑组件,而Verilog-A则扩展了这一能力,允许工程师模拟真实世界的物理效应,如电阻、电容、电感等模拟电路元素的行为。

实验的第一部分是Verilog-A模拟仿真。这部分可能包括了如何用Verilog-A编写模拟电路模型,以及如何进行仿真以验证这些模型的行为。例如,学生可能需要学习如何定义电路元件的参数,如电压、电流、频率响应等,并使用Verilog-A语法来描述这些元件之间的相互作用。

接下来,实验的第二部分是基于OCEAN的电路仿真。OCEAN是一个集成开发环境,它提供了与Cadence工具集的接口,用于混合信号和射频IC设计的仿真。在实验中,学生可能需要配置OCEAN的工作目录,拷贝必要的输入文件(如.ocn和_pvt.ocn文件),并运行仿真实验以测试他们的Verilog-A模型。输出文件被保存在预先创建的"outputfile"目录中,以便分析和讨论仿真结果。

在实际操作中,学生可能需要执行一系列命令,如`cd`来切换目录,`mkdir`来创建新目录,以及`cp`来复制文件到指定位置,这些都是在Linux或类Unix系统中常见的文件管理操作。这些步骤确保了学生能够在正确的环境中运行OCEAN仿真。

这个实验课程旨在提升学生对混合信号系统设计的理解,特别是通过使用Verilog-A描述模拟电路和利用OCEAN进行仿真的技能。这不仅要求学生具备基本的Verilog编程知识,还需要他们理解和应用模拟电路理论,以及熟悉相关的设计工具和流程。通过这样的实践,学生将能够更好地设计、验证和优化复杂的混合信号集成电路。

2021-05-09 上传

2022-09-21 上传

2022-09-24 上传

2022-09-23 上传

2022-09-23 上传

2022-09-21 上传

2012-03-20 上传

jokerxb3

- 粉丝: 1

- 资源: 16

最新资源

- 基于Python和Opencv的车牌识别系统实现

- 我的代码小部件库:统计、MySQL操作与树结构功能

- React初学者入门指南:快速构建并部署你的第一个应用

- Oddish:夜潜CSGO皮肤,智能爬虫技术解析

- 利用REST HaProxy实现haproxy.cfg配置的HTTP接口化

- LeetCode用例构造实践:CMake和GoogleTest的应用

- 快速搭建vulhub靶场:简化docker-compose与vulhub-master下载

- 天秤座术语表:glossariolibras项目安装与使用指南

- 从Vercel到Firebase的全栈Amazon克隆项目指南

- ANU PK大楼Studio 1的3D声效和Ambisonic技术体验

- C#实现的鼠标事件功能演示

- 掌握DP-10:LeetCode超级掉蛋与爆破气球

- C与SDL开发的游戏如何编译至WebAssembly平台

- CastorDOC开源应用程序:文档管理功能与Alfresco集成

- LeetCode用例构造与计算机科学基础:数据结构与设计模式

- 通过travis-nightly-builder实现自动化API与Rake任务构建