逆高斯分布驱动的亚阈值CMOS电路精准时序分析

需积分: 15 149 浏览量

更新于2024-07-15

收藏 818KB PDF 举报

随着现代电子技术的发展,特别是在低功耗和高性能要求驱动下,亚阈值CMOS电路的设计和优化变得越来越复杂。时序分析在这样的背景下显得尤为重要,因为它确保了芯片在实际应用中的性能和可靠性。传统的时延模型,如基于高斯分布(GD)的方法,可能无法准确地捕捉到电路在低电压和亚阈值操作下的动态行为。

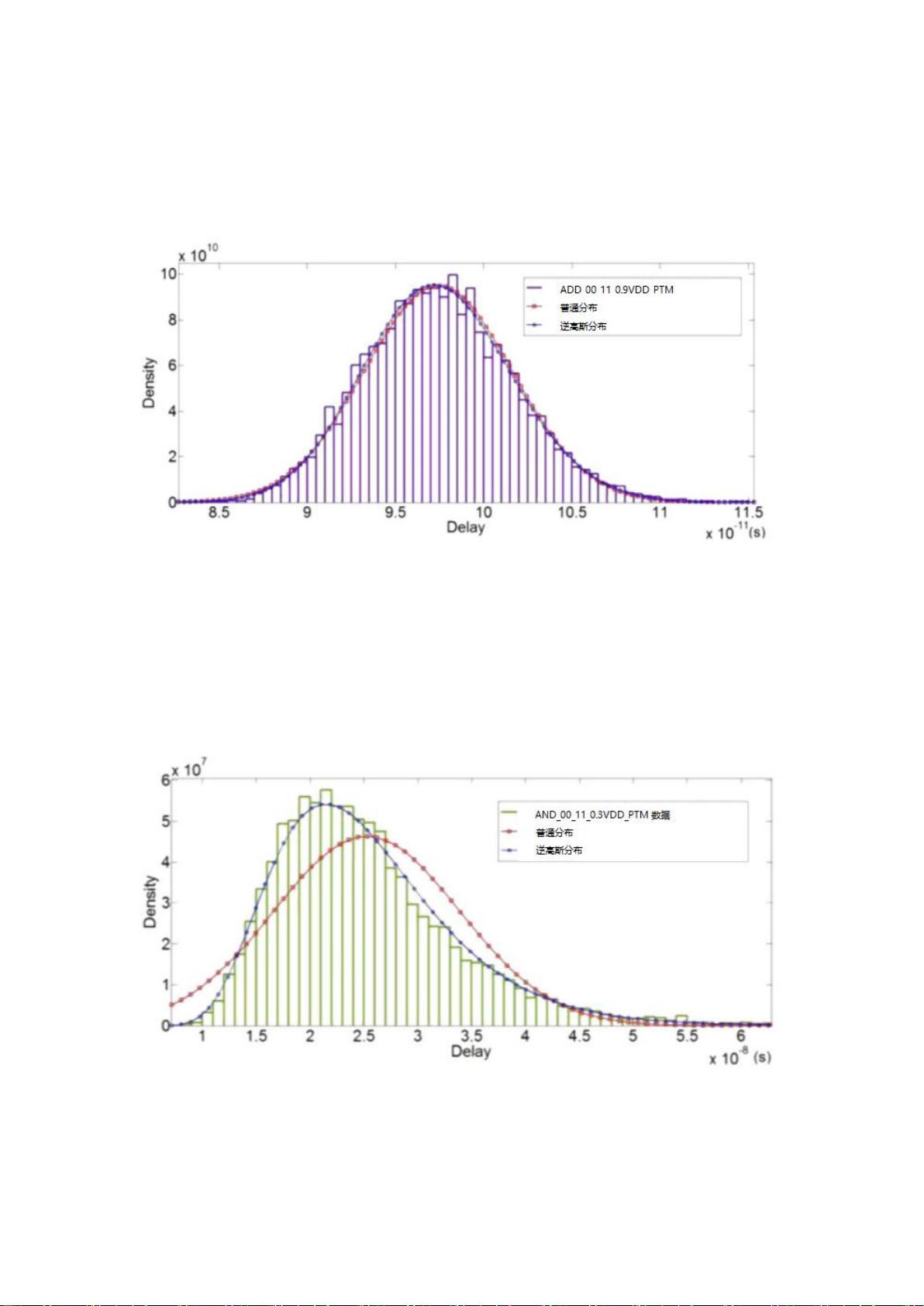

本文探讨了一种创新的时序分析策略,即基于逆高斯分布(IGD)的模型。逆高斯分布相较于正态分布,更适用于描述电路在极端条件下的非线性和不确定性。该模型的优势在于它能更好地处理由工艺参数变化、电压标度影响以及亚阈值效应带来的时延波动,尤其是在深亚微米工艺中,电路的敏感性和随机性使得传统的分析方法如角分析存在局限性。

作者通过比较基于IGD的延迟估计与HSPICE蒙特卡罗模拟的结果,验证了新模型的精度。实验结果显示,基于IGD的分析方法对于D触发器、8位纹波进位加法器、8位解复用器和多路复用器等多种电路组件的时序分析,其平均误差分别小于1.9%和1.2%,显著提高了估算的准确性。相比于GD模型,IGD模型在保持平均精度的同时,节省了大量的仿真时间,这对于设计者来说具有实际价值,因为他们能够在合理的时间范围内进行高效的设计迭代。

文章的关键点包括:

1. **亚阈值CMOS电路面临的挑战**:随着工艺发展,电路行为难以预测,尤其是当工作电压接近阈值电压时,功耗降低与性能下降并存。

2. **传统时序分析的局限**:高精度SPICE仿真是常用方法,但耗时长且可能无法适应设备的高敏感性。

3. **改进方法**:统计静态时序分析(SSTA)尝试解决自动化问题,但需考虑输入模式延迟依赖,且计算负担大。

4. **基于IGD的时序模型**:提出的新模型能够更精确地估计时延,减少误差,提高分析效率。

基于逆高斯分布的亚阈值CMOS电路时序分析为电子设计工程师提供了一个强大的工具,有助于他们更好地应对低功耗、高速度要求下的电路设计,提升数字集成电路的性能预测和优化能力。通过这种统计模型,设计师能够在快速迭代过程中确保电路在实际应用中的稳定性和有效性。

2022-11-11 上传

2021-07-13 上传

2023-03-21 上传

2024-08-31 上传

2024-10-16 上传

2024-06-15 上传

2023-06-02 上传

2024-06-08 上传

2023-06-12 上传

qq_33023953

- 粉丝: 5

- 资源: 4

最新资源

- WPF渲染层字符绘制原理探究及源代码解析

- 海康精简版监控软件:iVMS4200Lite版发布

- 自动化脚本在lspci-TV的应用介绍

- Chrome 81版本稳定版及匹配的chromedriver下载

- 深入解析Python推荐引擎与自然语言处理

- MATLAB数学建模算法程序包及案例数据

- Springboot人力资源管理系统:设计与功能

- STM32F4系列微控制器开发全面参考指南

- Python实现人脸识别的机器学习流程

- 基于STM32F103C8T6的HLW8032电量采集与解析方案

- Node.js高效MySQL驱动程序:mysqljs/mysql特性和配置

- 基于Python和大数据技术的电影推荐系统设计与实现

- 为ripro主题添加Live2D看板娘的后端资源教程

- 2022版PowerToys Everything插件升级,稳定运行无报错

- Map简易斗地主游戏实现方法介绍

- SJTU ICS Lab6 实验报告解析