RISC-V五级流水线CPU设计与实现

需积分: 0 12 浏览量

更新于2024-01-22

1

收藏 2.14MB PDF 举报

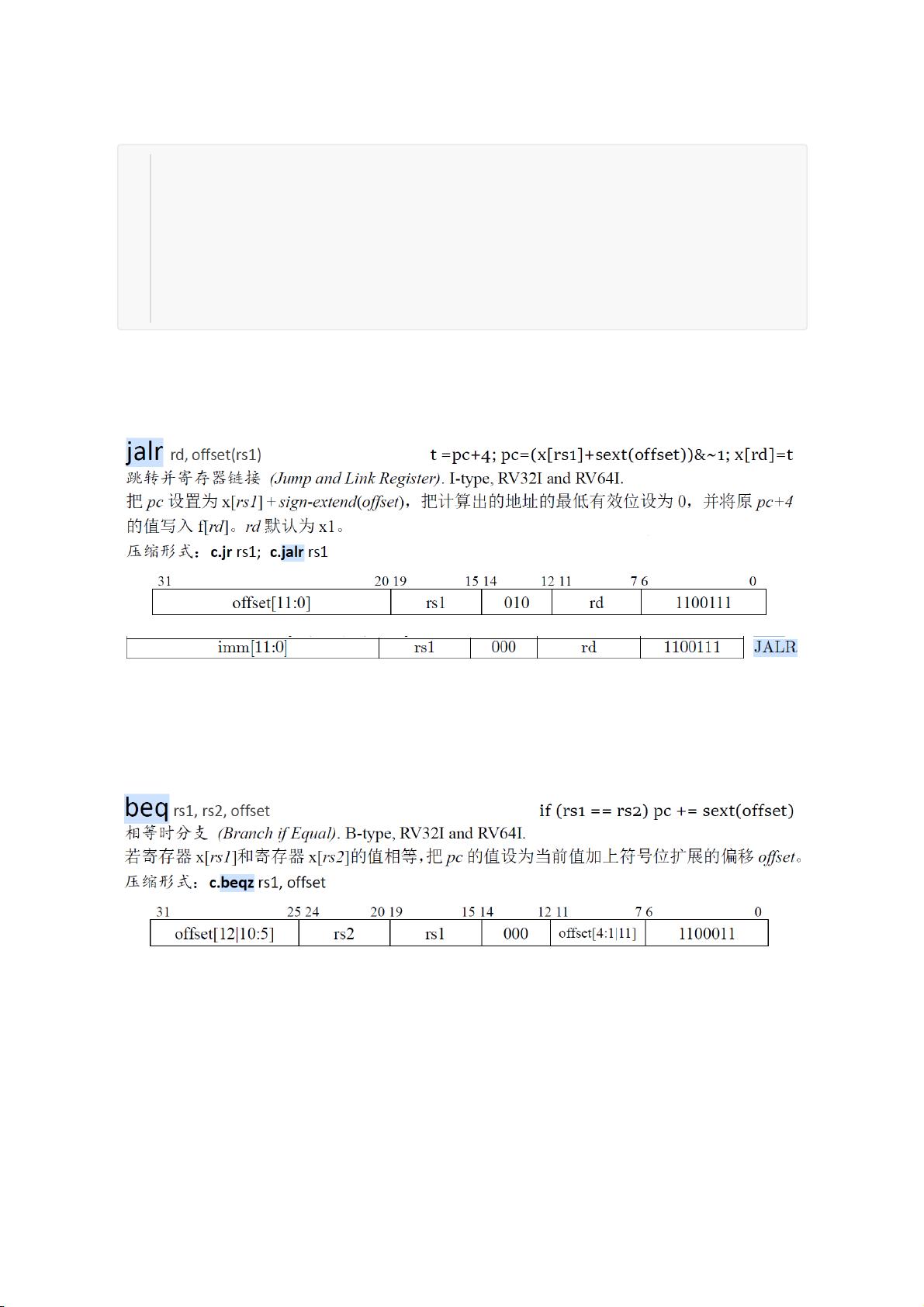

lab1分析与设计1;1、是否进行无条件跳转 ---- 由decode阶段产生2、是否进行条件跳转 ---- 由execute阶段产生1、对指令进行译码产生控制信号;lab 1分析与设计 lab 1最终需要实现一个基于RISC-V指令集的五级流水线cpu。本次实验中我的思路为(此部分为最终实现完成后回述): 首先分析待实现的指令,按照五级流水段划分的逻辑思路考虑指令在各阶段如何执行; 在对指令有一定了解后,结合指令需求分析各流水段依赖的信号,设计各级流水段的输入端口信号,并初步确定各级流水段的输出端口; 通过各模块输入端口信号依赖反推各级模块应该产生的输出信号; 综合信号在流水段间的产生与传输,确定各个模块的输出端口信号(此时端口基于单周期的数据通路设计),完成单周期实现; 确定流水线的数据部件结构为:五级流水段组合部件 流水寄存器部件; 分析流水寄存器连接后的流水线冒险与解决方式; 设计完善的流水寄存器(包括流水段之间的寄存器与处理冒险的寄存器); 完成连线,实现完整的流水线cpu;最终实现的五级流水线部件结构: 五级流水段的实现部件(基本组合逻辑),实现CPU的基本功能: 取指 ---- fetch,译码与访问regfile ---- decode,执行 ---- execute,访存 ---- memory,写回 ---- writeb;

在进行lab1的分析与设计时,首先需要理解要实现的五级流水线CPU的基本功能,即取指、译码与访问regfile、执行、访存和写回。通过对RISC-V指令集的分析,能够确定指令在各个阶段的执行方式。

在设计过程中,需要考虑各流水段之间的数据依赖关系,通过分析指令的需求来确定各级流水段的输入端口信号,并初步确定各级流水段的输出端口。这样就能够通过各模块的输入端口信号依赖来反推各级模块应该产生的输出信号。

在完成单周期实现之后,需要确定流水线的数据部件结构,包括五级流水段的组合部件和流水寄存器部件。这样能够在实现流水线时,准确传递信号并保证各个阶段的数据顺利传输。

同时,需要进行流水寄存器连接的分析,以解决流水线冒险问题。冒险问题可能包括数据冒险、控制冒险和结构冒险等。通过设计合理的流水寄存器,可以有效解决冒险问题,保证流水线的正常运行。

最后,完成连线,实现完整的流水线CPU。通过连接各个部件,能够使整个CPU能够按照设计要求进行正常的工作。最终实现的五级流水线部件结构包括了取指、译码与访问regfile、执行、访存和写回五个基本功能的实现部件。这些实现部件通过基本的组合逻辑,能够使CPU能够正常执行指令。

通过以上的分析与设计过程,能够实现一个基于RISC-V指令集的五级流水线CPU。这个CPU能够在执行指令时,实现取指、译码与访问regfile、执行、访存和写回等功能。在实现过程中,需要考虑各个阶段之间的数据依赖关系和冒险问题,并设计合理的流水寄存器来解决这些问题。最终通过连接各个部件,能够实现一个完整的流水线CPU。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-03-30 上传

802 浏览量

2022-08-03 上传

2022-08-03 上传

2021-03-28 上传

2021-03-31 上传

黄浦江畔的夏先生

- 粉丝: 18

最新资源

- 理解AJAX基础与实现

- BEA Tuxedo精华贴总结:程序示例与环境变量设置

- TUXEDO函数详解:tpalloc, tprealloc, tpfree, tptypes与FML操作

- Windows CE预制平台SDK掌上电脑1.1中文版使用指南

- 21DT数控车床编程指南:操作与编程指令详解

- 随机化算法:原理、设计与应用探索

- PB编程入门:核心函数详解与知识架构构建

- Ant实战教程:从入门到精通

- DB2 SQL语法指南:从创建到索引详解

- Java GUI设计入门:AWT与Swing解析

- VCL 7.0继承关系详解:完整对象树与可用版本区分

- 十天精通ASP.NET:从安装到实战

- 有效软件测试的关键策略

- ARM ADS1.2开发环境与AXD调试教程

- 详述JSTL:核心、I18N、SQL与XML标签库解析

- ×××论坛系统概要设计说明书