ALTERA FPGA基础时序分析:寄存器路径详解与约束策略

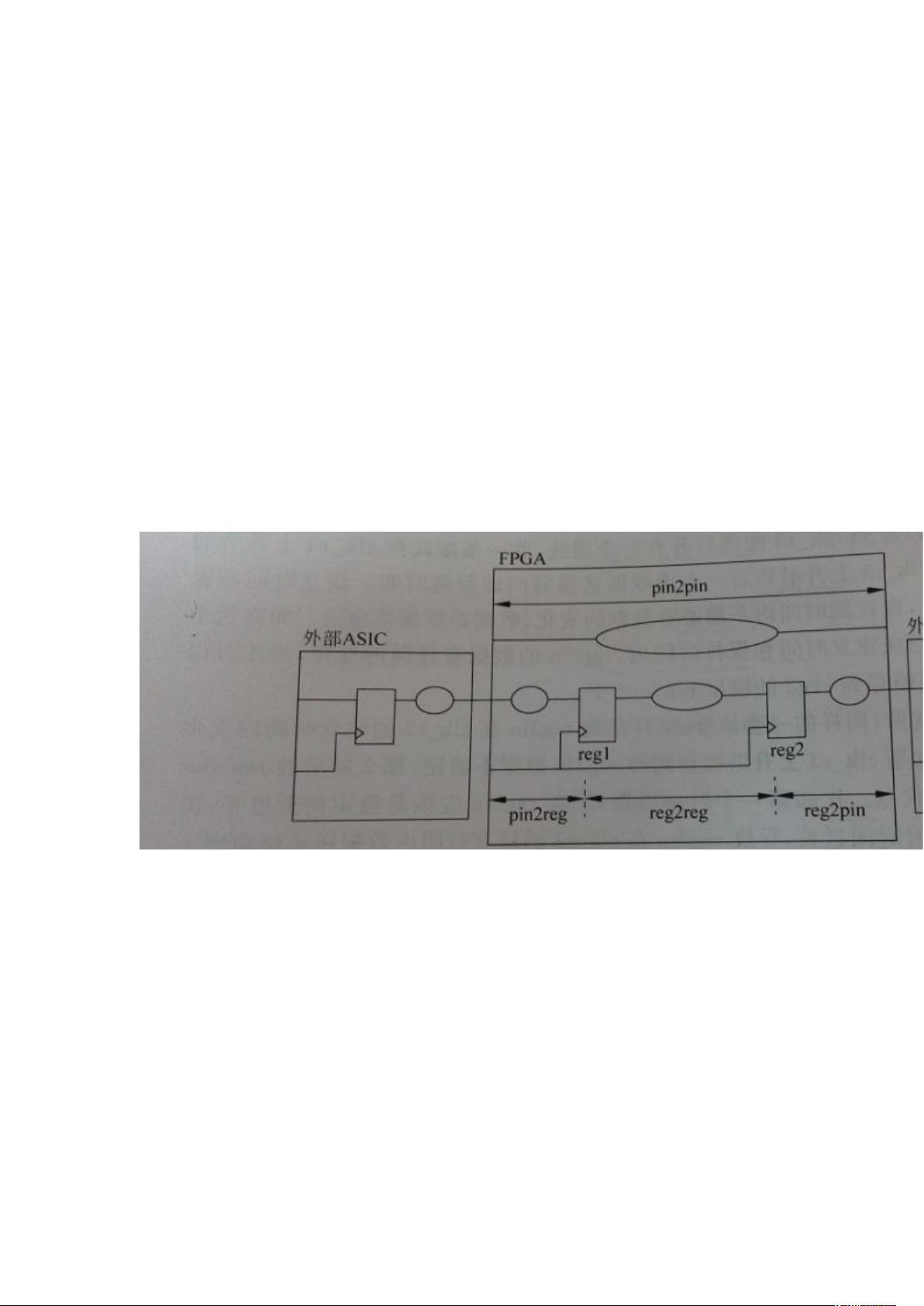

ALTERA系列的FPGA时序分析着重于理解FPGA内部的基本时序路径,这些路径主要包括内部寄存器之间的(reg2reg),输入引脚到内部寄存器(pin2reg),内部寄存器到输出引脚(reg2pin),以及输入引脚到输出引脚(pin2pin)的路径。其中,reg2reg、pin2reg和reg2pin路径由于涉及到时钟信号,分析时需要关注数据信号与时钟沿的建立时间和保存时间,以确保信号的正确同步。而对于pin2pin路径,因为信号不通过时钟,其约束相对简单,主要是确定信号延时的范围。

在约束这些时序路径时,有不同的方法。对于reg2reg,用户需提供时钟频率,时序约束工具会根据这个信息确保路径延迟在时钟周期范围内,保证Setup Slack和Hold Slack的正值。pin2reg约束需要参考芯片数据手册中的延迟参数,如Tco、Tsu和Th,并可能通过将pin2reg视为内部reg2reg路径的一部分来进行。同样,reg2pin的约束也是基于芯片提供的引脚特性。

对于pin2pin路径,主要关注信号的实际传输延时,无需考虑建立时间和保持时间,只需提供最大和最小的延时值给时序设计工具。计算这些路径的Setup Slack和Hold Slack是确保设计稳定性的关键,这可以通过使用预设的公式或者工具自动计算得出。

总结起来,ALTERA系列FPGA时序分析涉及到了对内部信号流的精确控制,包括了解不同路径的工作原理,正确使用芯片数据手册提供的信息,以及有效应用时序约束工具来确保设计满足时序要求。这对于优化FPGA性能,避免潜在的设计问题至关重要。

137 浏览量

141 浏览量

169 浏览量

2024-11-06 上传

139 浏览量

191 浏览量

2024-10-29 上传

2024-11-06 上传

2024-10-29 上传