- 8 -

四.FL6410主要硬件设计说明

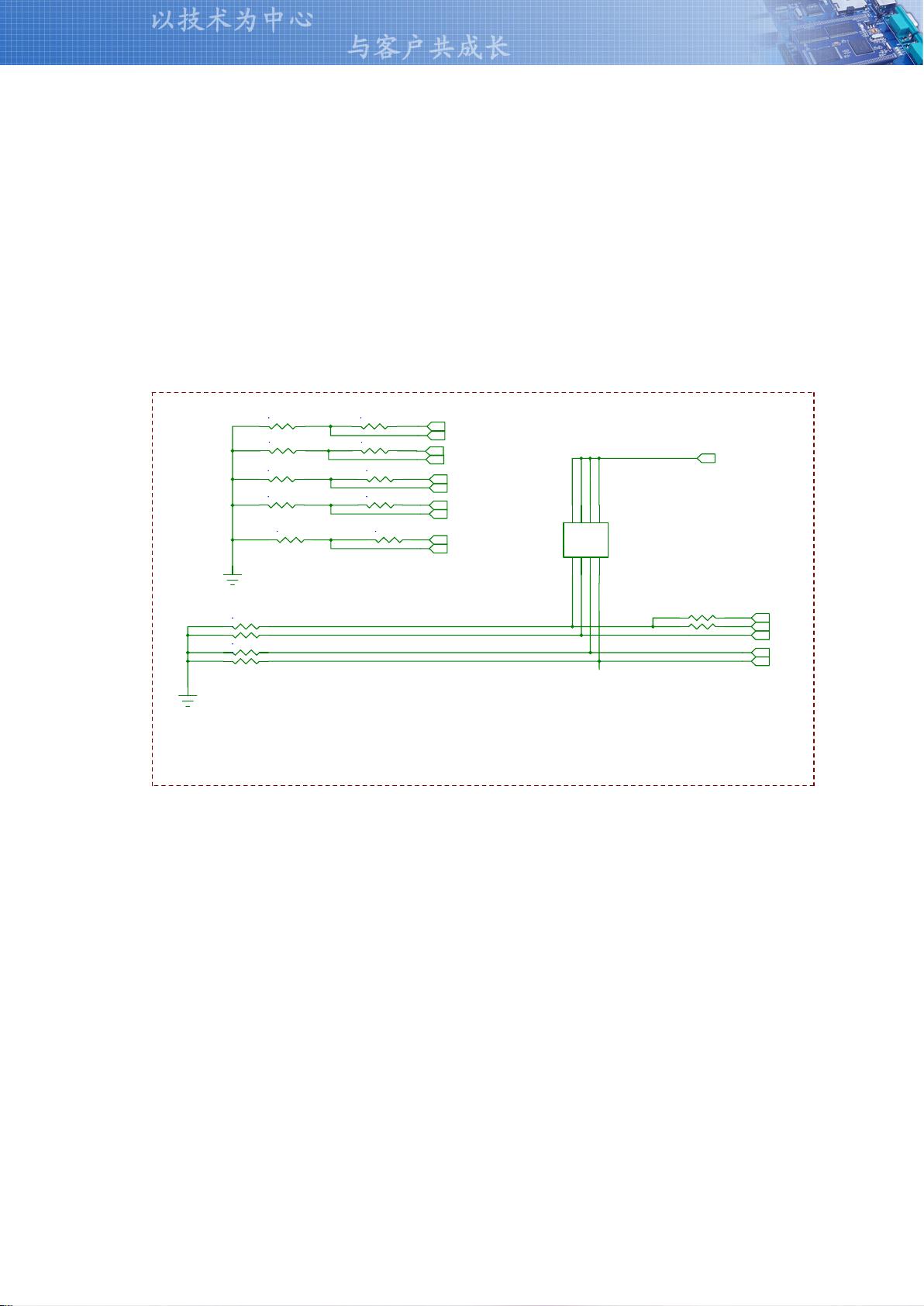

1.NAND FLASH

FL6410开发板配置256M Bytes NAND FLASH,型号为K9F2G08U0B(另有MLC

结构2G Bytes NAND FLASH的K9GAG08U0D供用户选择),片选信号使用CSn2。

NAND FLASH 存储器主要用于存放内核代码、应用程序、文件系统和数据资料。

注:FL6410开发板使用NAND FLASH存储器,当使用NAND FLASH 启动时,

S3C6410处理器同时配置了CSn2、CSn3为NAND FLASH存储器片选信号,因此在

这种情况下CSn3不可以连接NAND FLASH以外的总线设备。

NAND FLASH设计原理图:

NOR FLASH

HOME:

FL6410 Board

COMPANY:

Forlinx Embedded

TITLE:

www.witech.com.cn

DDRAM SELECT

256M SEKCET R36 ( R21,R22,R23 NC)

128M (R36,R21,R22,R23 NC)

NAND FLASH

1

NC1

2

NC2

3

NC3

4

NC4

5

NC5

11

NC6

14

NC7

29

I/O0

30

I/O1

31

I/O2

32

I/O3

41

I/O4

42

I/O5

43

I/O6

44

I/O7

9

CE1

10

CE2

18

WE

8

RE

16

CLE

17

ALE

7

R/B1

6

R/B2

15

NC8

20

NC9

21

NC10

22

NC11

23

NC12

24

NC13

25

NC14

26

NC15

27

NC16

28

NC17

33

NC18

34

NC19

35

NC20

38

NC21

39

NC22

40

NC23

45

NC24

46

NC25

47

NC26

48

NC27

12

VCC1

37

VCC2

13

VSS1

19

/WP

36

VSS2

U3

K9GAG08

1

2

R17

10R

R18

10R

R19

4.7k

R20

4.7k

C55

0.1u

C57

0.1u

+

C56

10u

+

C58

10u

C59

0.1u

C60

0.1u

C61

0.1u

C62

0.1u

C63

0.1u

C64

0.1u

C65

0.1u

C66

0.1u

C67

0.1u

C68

0.1u

C69

0.1u

C70

0.1u

J8

A0

J9

A1

K7

A2

K8

A3

K2

A4

K3

A5

J1

A6

J2

A7

J3

A8

H1

A9

J7

A10

H2

A11

H3

A12

H8

BA0

H9

BA1

G2

CK

G3

CK

G9

RAS

G8

/CAS

G7

/WE

H7

/CS0

G1

CKE0

F3

NC/CKE1

F7

NC/CS1

B1

VDDQ1

D1

VDDQ2

A7

VDDQ3

C9

VDDQ4

E9

VDDQ5

A9

VDD1

F9

VDD2

K9

VDD3

A8

DQ0

B7

DQ1

B8

DQ2

C7

DQ3

C8

DQ4

D7

DQ5

D8

DQ6

E7

DQ7

E3

DQ8

D2

DQ9

D3

DQ10

C2

DQ11

C3

DQ12

B2

DQ13

B3

DQ14

A2

DQ15

E8

LDQS

E2

UDQS

F8

LDM

F2

UDM

A3

VSSQ1

C1

VSSQ2

E1

VSSQ3

B9

VSSQ4

D9

VSSQ5

A1

VSS1

F1

VSS2

K1

VSS3

U11

K4X51163PEL

J8

A0

J9

A1

K7

A2

K8

A3

K2

A4

K3

A5

J1

A6

J2

A7

J3

A8

H1

A9

J7

A10

H2

A11

H3

A12

H8

BA0

H9

BA1

G2

CK

G3

CK

G9

RAS

G8

/CAS

G7

/WE

H7

/CS0

G1

CKE0

F3

NC/CKE1

F7

NC/CS1

B1

VDDQ1

D1

VDDQ2

A7

VDDQ3

C9

VDDQ4

E9

VDDQ5

A9

VDD1

F9

VDD2

K9

VDD3

A8

DQ0

B7

DQ1

B8

DQ2

C7

DQ3

C8

DQ4

D7

DQ5

D8

DQ6

E7

DQ7

E3

DQ8

D2

DQ9

D3

DQ10

C2

DQ11

C3

DQ12

B2

DQ13

B3

DQ14

A2

DQ15

E8

LDQS

E2

UDQS

F8

LDM

F2

UDM

A3

VSSQ1

C1

VSSQ2

E1

VSSQ3

B9

VSSQ4

D9

VSSQ5

A1

VSS1

F1

VSS2

K1

VSS3

U13

K4X51163PEL

R21

10R

R22

10R

R23

10R

R36

10R

48

A16

17

A17

16

A18

25

A0

24

A1

23

A2

22

A3

21

A4

20

A5

19

A6

18

A7

8

A8

7

A9

6

A10

5

A11

4

A12

3

A13

2

A14

1

A15

9

A19

10

NC3

13

NC2

14

NC1

27

VSS1

46

VSS0

29

DQ0

31

DQ1

33

DQ2

35

DQ3

38

DQ4

40

DQ5

42

DQ6

44

DQ7

30

DQ8

32

DQ9

34

DQ10

36

DQ11

39

DQ12

41

DQ13

43

DQ14

45

DQ15/A-1

26

NCE

28

NOE

11

NWE

15

NRY/BY

12

NRESET

47

NBYTE

37

VDD

U24

AM29LV160DB

R141

0¦¸

DATA[0:15]

DATA0

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

CSN2

CSN3

FWEN

FREN

FCLE

FALE

RNB

VDD_IO

VDD_IO

VDD_MDDR

XM1_ADDR[0:15]

XM1_ADDR0

XM1_ADDR1

XM1_ADDR2

XM1_ADDR3

XM1_ADDR4

XM1_ADDR5

XM1_ADDR6

XM1_ADDR7

XM1_ADDR8

XM1_ADDR9

XM1_ADDR10

XM1_ADDR11

XM1_ADDR12

XM1_ADDR14

XM1_ADDR15

XM1_SCLK

XM1_SCLKN

XM1_RASN

XM1_CASN

XM1_WEN

XM1_CSN0

XM1_CKE0

VDD_MDDR

XM1_ADDR[0:15]

XM1_ADDR0

XM1_ADDR1

XM1_ADDR2

XM1_ADDR3

XM1_ADDR4

XM1_ADDR5

XM1_ADDR6

XM1_ADDR7

XM1_ADDR8

XM1_ADDR9

XM1_ADDR10

XM1_ADDR11

XM1_ADDR12

XM1_ADDR14

XM1_ADDR15

XM1_SCLK

XM1_SCLKN

XM1_RASN

XM1_CASN

XM1_WEN

XM1_CSN0

XM1_CKE0

VDD_MDDR

XM1_DQS0

XM1_DQS1

XM1_DQM0

XM1_DQM1

XM1_DATA[0:15]

XM1_DATA0

XM1_DATA1

XM1_DATA2

XM1_DATA3

XM1_DATA4

XM1_DATA5

XM1_DATA6

XM1_DATA7

XM1_DATA8

XM1_DATA9

XM1_DATA10

XM1_DATA11

XM1_DATA12

XM1_DATA13

XM1_DATA14

XM1_DATA15

XM1_DQS2

XM1_DQS3

XM1_DQM2

XM1_DQM3

XM1_DATA[16:31]

XM1_DATA16

XM1_DATA17

XM1_DATA18

XM1_DATA19

XM1_DATA20

XM1_DATA21

XM1_DATA22

XM1_DATA23

XM1_DATA24

XM1_DATA25

XM1_DATA26

XM1_DATA27

XM1_DATA28

XM1_DATA29

XM1_DATA30

XM1_DATA31

XM1_CKE0

XM1_CKE1

XM1_CSN1

XM1_ADDR13

MDDR_CKE1

MDDR_CSN1

MDDR_CKE1

MDDR_CSN1

MDDR_CKE1

MDDR_CSN1

ADDR[1:15]

ADDR1

ADDR2

ADDR3

ADDR4

ADDR5

ADDR6

ADDR7

ADDR8

ADDR9

ADDR10

ADDR11

ADDR12

ADDR13

ADDR14

ADDR15

ADDR16

ADDR17

ADDR18

ADDR19

DATA[0:15]

DATA0

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

DATA8

DATA9

DATA10

DATA11

DATA12

DATA13

DATA14

DATA15

CSN0

OEN

WEN

XNRSTOUT

VDD_IO

VDD_IO