Verilog实现RS232串口通信及电平转换

"该资源主要介绍了如何在Verilog中实现RS232串口通信,并涉及到FPGA学习的相关内容。通过Verilog代码实现RS232通信,包括重要的管脚定义、通信时序、电平转换以及波特率的理解。"

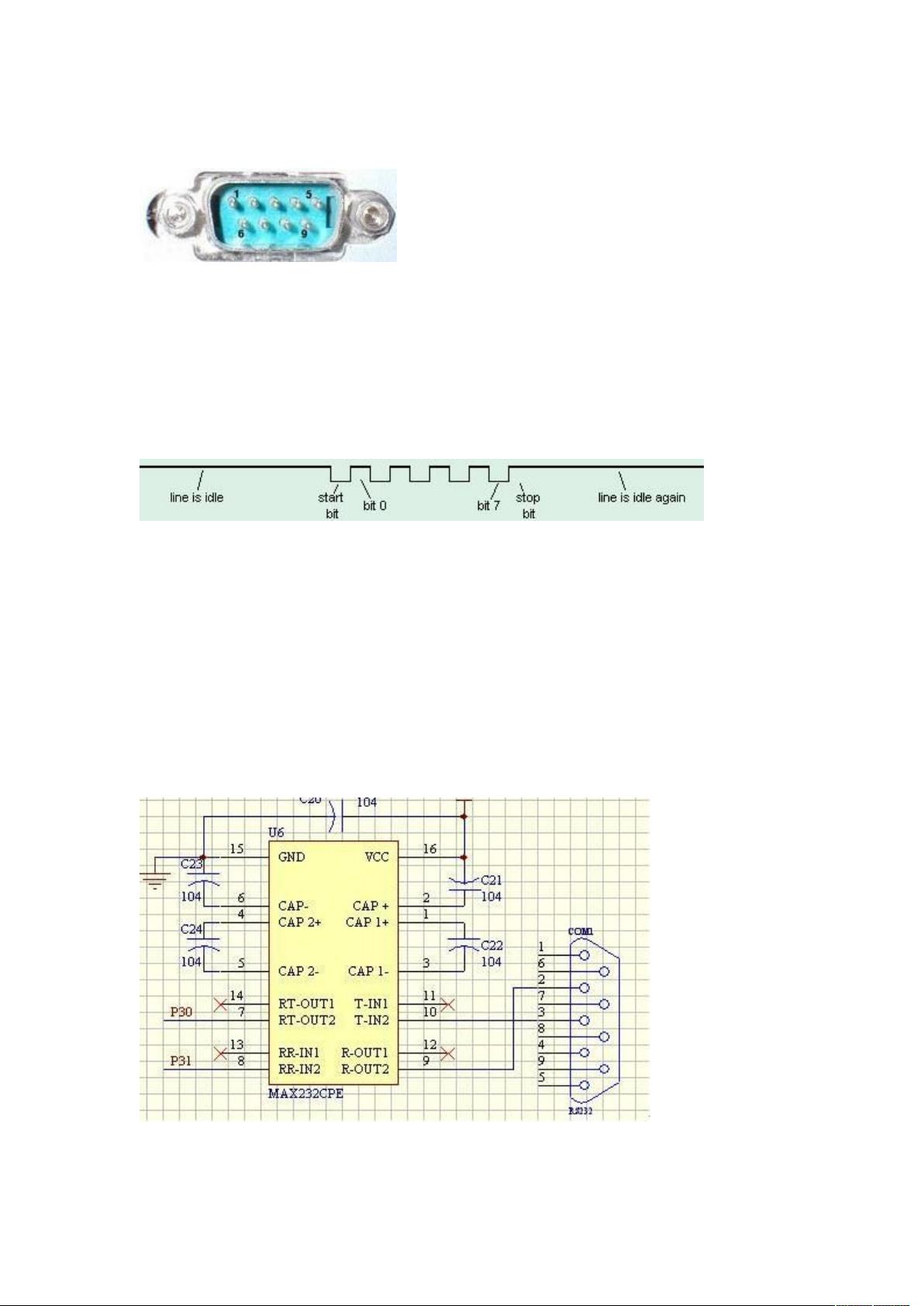

在串口通信中,RS232是一种广泛使用的标准,它定义了接口的电气特性以及信号的传输方式。在Verilog中实现RS232通信,首先需要理解其关键的管脚功能。pin2(RxD)是接收数据端,pin3(TxD)是发送数据端,而pin5(GND)则是接地。在发送数据时,例如0x55,由于Verilog遵循低字节优先原则,因此发送顺序是1-0-1-0-1-0-1-0。

RS232电平标准规定,“1”状态通常由-10V至-15V的电压表示,“0”状态则由+10V至+15V的电压表示。由于计算机内部的RS232电平与FPGA等电路板上的电源电平不匹配,因此需要使用转换芯片进行电平转换。例如,如果电路板电源为±5V,可以使用MAX232;如果是±3.3V,则应使用MAX3232。

在实际布线时,需注意RS232的线缆连接,如采用母头,需使用交叉线,确保电路板的RxD连接到计算机的TxD,电路板的TxD连接到计算机的RxD。

串行通信中的波特率和比特率是两个关键概念。比特率是指数字信号传输速率,以单位时间内传输的二进制位数表示,单位通常为bps、Kbps或Mbps。波特率则表示数据信号对载波的调制速率,单位是波特。在两相调制中,每个调制状态对应1个二进制位,因此波特率与比特率相等。例如,如果系统时钟为1.8432MHz,16分频后得到115200Hz的波特率,即比特率。

在实际应用中,系统时钟可能不恰好是波特率的整数倍。在这种情况下,可以通过软件或硬件方法来调整波特率生成,如在Verilog代码中实现波特率发生器。如果系统时钟为2MHz,可以设计相应的逻辑来产生所需的波特率,如115200bps,这通常涉及到计数器和分频器的设计。

这个资源提供了关于RS232串口通信的Verilog实现细节,包括管脚定义、电平转换、波特率计算和实现,对于FPGA学习者来说是非常有价值的参考资料。

2010-07-27 上传

2014-12-15 上传

2012-07-21 上传

2018-05-15 上传

2018-05-07 上传

2020-05-14 上传

2022-09-19 上传

2013-09-16 上传

2016-12-14 上传