Altera FIFO与SignalTap II问题深度解析

需积分: 12 11 浏览量

更新于2024-07-22

收藏 1.46MB PDF 举报

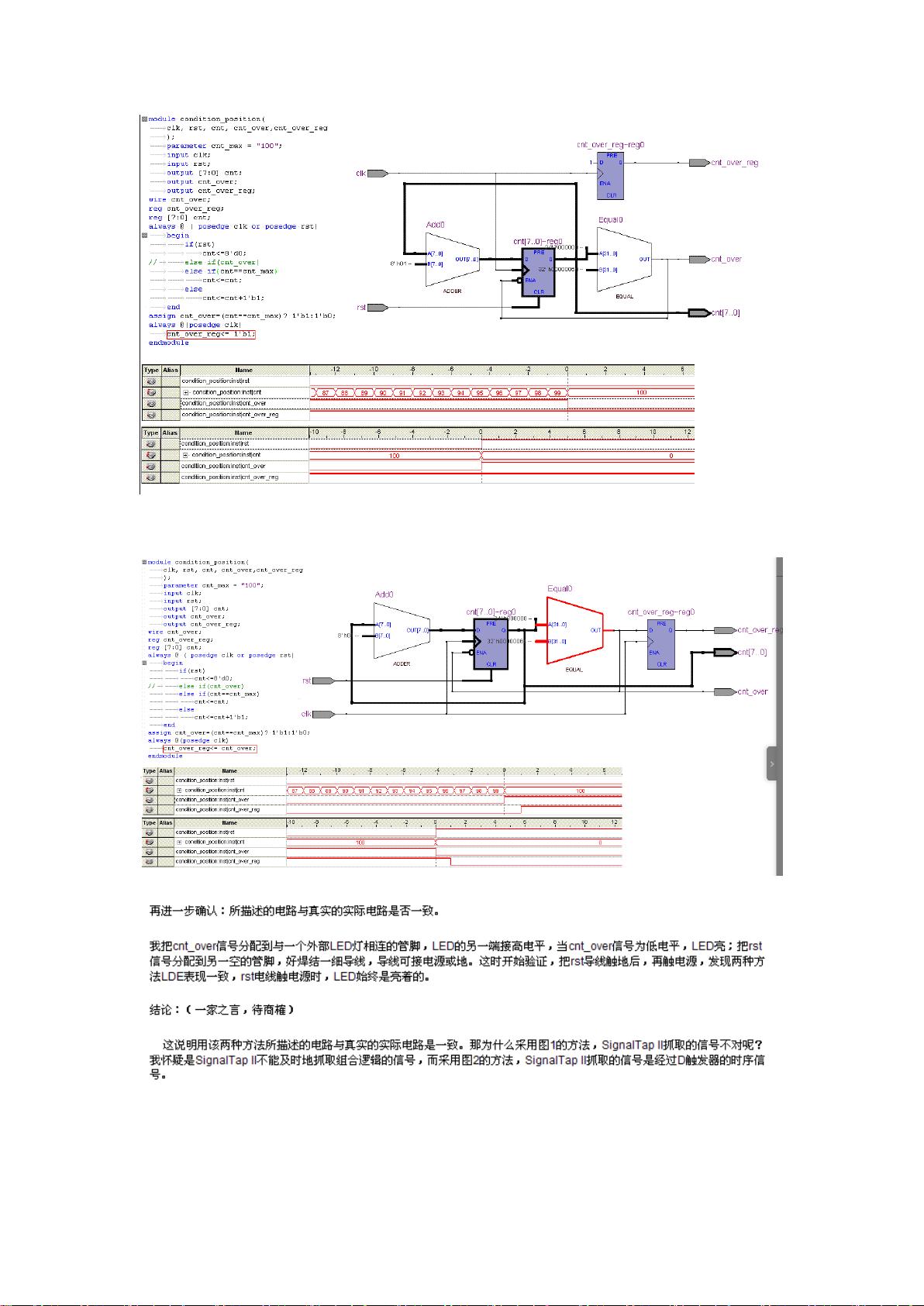

本文档由作者Weizhiheng99@foxmail.com,博客名为赤松子耶,主要聚焦于Altera FPGA中的fifo问题和Signaltap II故障分析。首先,作者分享了一个关于Altardcfifo读写顺序的问题,图片显示了在使用Signaltap II时遇到的异常情况。Signaltap II是一个嵌入式逻辑分析工具,它在设计的网表中添加触发逻辑、存储逻辑以及用于与PC通信的虚拟JTAG链路,从而实现逻辑分析功能。然而,这个过程可能导致资源抢占,特别是逻辑元素(LE)和内存块(MB),这被称为"测不准原理"。

作者指出,当在FPGA设计中集成Signaltap II时,可能会出现编译前后行为差异的情况。这种差异可能源于以下几点原因:

1. Signaltap工具潜在的bug:虽然未得到证实,但作者推测Signaltap的内部实现可能含有bug,由于用户无法控制插入过程,可能导致设计的初衷被违背。

2. 信号扇出扩大:为了实现信号的实时监控,Signaltap需要在信号路径中插入触发器和组合逻辑,这会增加信号的扇出,从而可能改变信号的输出延迟。如果信号原本时序紧张,额外的延迟可能改善(减少)时序问题,反之则可能导致新的或更频繁的时序问题。

3. 资源抢占导致时序变化:Signaltap的添加会影响设计的时序余量,特别是在资源有限的FPGA中,可能导致设计性能下降或新的问题。

4. 调试过程的干扰:观察信号实际上是在干预信号的行为,这可能会无意中改变设计的动态行为,表现为bug消失或新bug的出现。

这篇文章提供了Signaltap II在Altera FPGA应用中可能遇到的问题及其背后的原因分析,这对于理解如何有效使用Signaltap II进行调试,并避免或减轻其对设计性能的影响具有参考价值。在实际设计过程中,理解和管理这些潜在影响是至关重要的。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-09-19 上传

2022-09-14 上传

2022-09-23 上传

2022-09-22 上传

2022-09-20 上传

2022-09-20 上传

zbtc2007

- 粉丝: 0

- 资源: 2

最新资源

- Angular程序高效加载与展示海量Excel数据技巧

- Argos客户端开发流程及Vue配置指南

- 基于源码的PHP Webshell审查工具介绍

- Mina任务部署Rpush教程与实践指南

- 密歇根大学主题新标签页壁纸与多功能扩展

- Golang编程入门:基础代码学习教程

- Aplysia吸引子分析MATLAB代码套件解读

- 程序性竞争问题解决实践指南

- lyra: Rust语言实现的特征提取POC功能

- Chrome扩展:NBA全明星新标签壁纸

- 探索通用Lisp用户空间文件系统clufs_0.7

- dheap: Haxe实现的高效D-ary堆算法

- 利用BladeRF实现简易VNA频率响应分析工具

- 深度解析Amazon SQS在C#中的应用实践

- 正义联盟计划管理系统:udemy-heroes-demo-09

- JavaScript语法jsonpointer替代实现介绍