FPGA实现的多相滤波数字接收机:高效信道化与FPGA优势

181 浏览量

更新于2024-09-01

收藏 546KB PDF 举报

本文主要探讨了EDA/PLD中基于多相滤波的数字接收机在FPGA上的实现策略。首先,引言部分阐述了信道化接收机的重要性,它是针对传统并行多通道接收机存在的设备复杂、性能不一致和可靠性问题而提出的解决方案。数字信道化接收机具有显著优势,如高瞬时带宽、灵敏度、动态范围以及信号处理能力,但直接信道化方法的运算量大,输出速率与采样速率同步,这对FPGA这样的信号处理器构成了挑战,因为它无法高效处理高速信号。

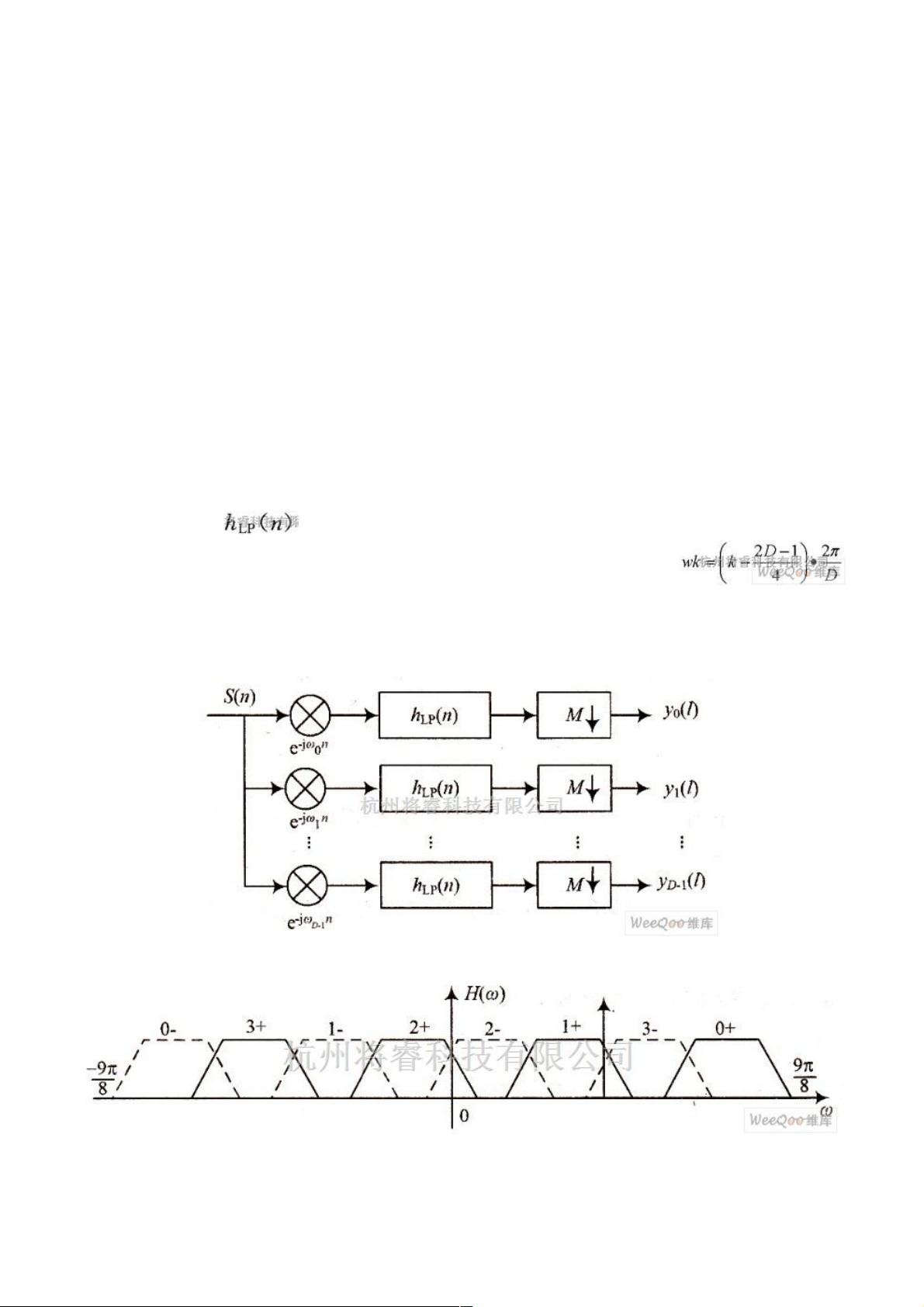

传统的直接信道化接收机在设计上面临输出速率过快的问题,这使得在单片FPGA上实现变得困难。相比之下,基于多相滤波的信道化接收机在滤波前进行抽取,大大减少了运算量,降低了输出速率,从而使得在FPGA上实现数字信道化成为可能。这种方法允许接收机在一片FPGA中实现宽带处理,如875MHz的系统带宽(62.5~937.5MHz),能同时处理两个信号并实时提供参数测量,如功率峰值指示(PDW)。

文章接下来详细描述了宽带数字接收机的结构,其中数字信道化的原理核心在于将信号划分为多个子频段,通过低通滤波器和抽取技术降低输出速率。然而,这一过程会引入频谱混叠现象,导致信道的虚假输出。为解决这个问题,文中提及了利用信道频率重叠的方法来连续覆盖整个瞬时带宽,并运用Rife算法进行测频,通过利用信道重叠特性,有效地消除了虚假信号。

本文提供了在FPGA中设计和实现基于多相滤波的数字接收机的有效途径,强调了这种技术在克服传统接收机难题,提高信号处理效率和精度方面的价值。对于从事EDA/PLD设计和信号处理领域的工程师来说,理解和掌握这些技术对于提升接收机性能和优化硬件资源分配至关重要。

487 浏览量

246 浏览量

196 浏览量

116 浏览量

171 浏览量

106 浏览量

164 浏览量

2020-11-08 上传

117 浏览量

weixin_38637878

- 粉丝: 3

最新资源

- 初学者入门必备!Visual C++开发的连连看小程序

- C#实现SqlServer分页存储过程示例分析

- 西门子工业网络通信例程解读与实践

- JavaScript实现表格变色与选中效果指南

- MVP与Retrofit2.0相结合的登录示例教程

- MFC实现透明泡泡效果与文件操作教程

- 探索Delphi ERP框架的核心功能与应用案例

- 爱尔兰COVID-19案例数据分析与可视化

- 提升效率的三维石头制作插件

- 人脸C++识别系统实现:源码与测试包

- MishMash Hackathon:Python编程马拉松盛事

- JavaScript Switch语句练习指南:简洁注释详解

- C语言实现的通讯录管理系统设计教程

- ASP.net实现用户登录注册功能模块详解

- 吉时利2000数据读取与分析教程

- 钻石画软件:从设计到生产的高效解决方案