FPGA实验:数码管动态扫描电路设计与实现

需积分: 0 44 浏览量

更新于2024-08-05

1

收藏 351KB PDF 举报

"《数字电路与逻辑设计实验A》实验三 基于FPGA的动态扫描电路设计2020-2021(1)1"

在本次实验中,主要目标是深入理解并实践数字电路与逻辑设计,特别是与FPGA(Field-Programmable Gate Array)相关的技术。实验内容涵盖了数码管显示原理、静态和动态扫描电路设计,以及FPGA设计文件的调用和整合。

实验目的:

1. 熟悉7段数码管的显示译码电路设计,理解数码管如何通过不同的电流路径显示数字。

2. 掌握数码管的静态和动态扫描显示原理,了解如何减少电源消耗并提高显示刷新率。

3. 通过实际操作,学习如何利用FPGA硬件平台实现数码管的静态和动态显示。

实验任务:

1. 利用FPGA硬件平台上的4位数码管进行静态显示,通过SW0-3输入BCD码,SW4-7控制数码管位选,实现数字的直观显示。

2. 设计一个模10计数器,使用FPGA实现其结果在4位数码管上以静态方式显示,每1秒更新一次。

3. 在6位数码管上实现动态显示,显示模100计数结果,同样以1秒为周期更新,动态扫描技术能有效减少硬件资源的占用。

任务1指导:

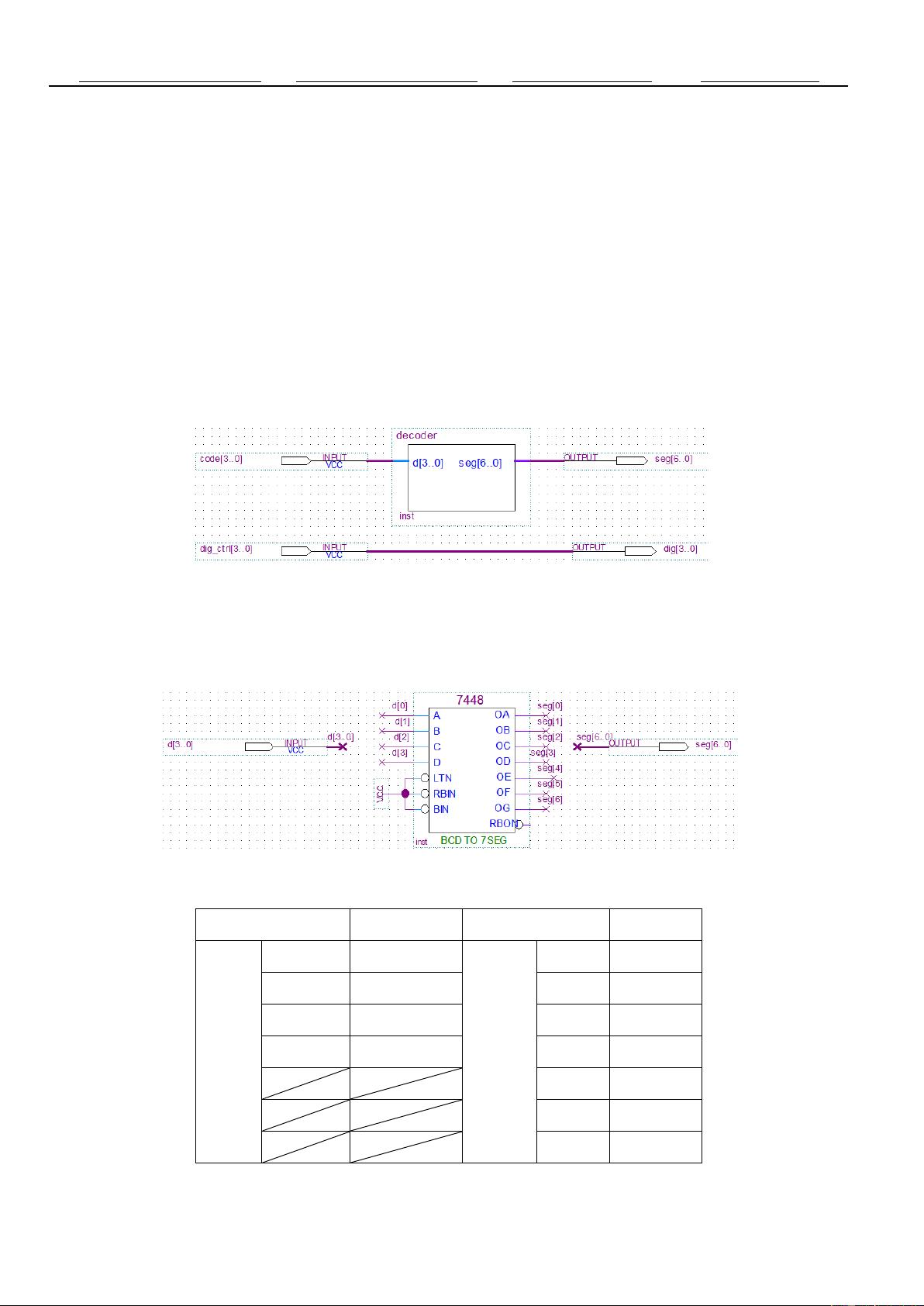

1. 任务1的顶层电路设计包含了数码管的段选和位选控制,解码器模块如7448用于将8421BCD码转换为七段码,驱动数码管显示数字。设计时需要锁定各个输入输出引脚,例如数据输入端code和数码管的段选端seg,以及位选控制端dig_ctrl。

2. decoder模块设计是关键,7448是一个共阴极译码器,能将BCD码转化为适合共阴极数码管的段码,实现十进制数字的显示。

任务2指导:

1. 任务2要求集成之前设计的秒信号产生模块(fre_div)、模10计数模块(cnt10)和译码显示模块(decoder)。秒信号模块将50MHz的时钟信号分频为1Hz,作为模10计数模块的时钟源,计数范围从0000到1001,计数值送入译码模块,产生相应的段码。

2. 调用已有设计文件时,需将原理图文件(.bdf)和symbol文件复制到工程目录下,并在工程中添加这些文件,确保所有相关设计文件都已包含。

通过这个实验,学生将不仅学习到基本的数码管显示技术和FPGA编程,还能锻炼在实际项目中整合和调用已有设计的能力,这对于提升 FPGA 开发技能和系统级设计理解至关重要。同时,实验也强调了文件管理和工程组织的重要性,这对今后的工程实践非常有益。

200 浏览量

120 浏览量

821 浏览量

2024-11-06 上传

2024-12-30 上传

2024-11-07 上传

179 浏览量

117 浏览量

2024-10-30 上传

吉利吉利

- 粉丝: 29

最新资源

- MCS-51单片机驱动的多通道温度监控与报警系统

- 综合布线系统设计基础知识要点

- 南开大学计算机数据库技术:素数筛选与四位数素数计数

- Boson NetSim CCNP路由器实验:配置与路由协议实践

- 使用Flash创建放大镜效果动画教程

- C#序列化与反序列化详解:实例与比较

- Ajax实战中文版:开创Web设计新篇章

- MODBUS TCP/IP 实施指南

- 华为H3C考试题库与网络工程师认证指南

- ARM嵌入式入门教程:从基础知识到实践实验

- Modbus协议详解:从入门到精通

- Java分布式计算在Applet中的应用与CORBA服务详解

- 电子商务系统用户驱动需求详解:功能与角色需求分析

- C语言编程:组合数字与奖金计算算法

- 中文全文检索技术:算法研究与系统实现

- 软件工程:数据流图与实体联系图示例解析