华为Verilog HDL入门教程:结构与语法详解

下载需积分: 44 | PDF格式 | 281KB |

更新于2024-07-29

| 102 浏览量 | 举报

Verilog HDL 华为入门教程是一份内部公开的详细指南,专为初学者设计,旨在教授Verilog Hardware Description Language(HDL)的基础知识。该教程共41页,涵盖了Verilog HDL的核心概念、语法结构和实际应用。

1. 章节概览:

- 第1章介绍了Verilog HDL的基本概念,包括定义、书写规范和常用的关键字。

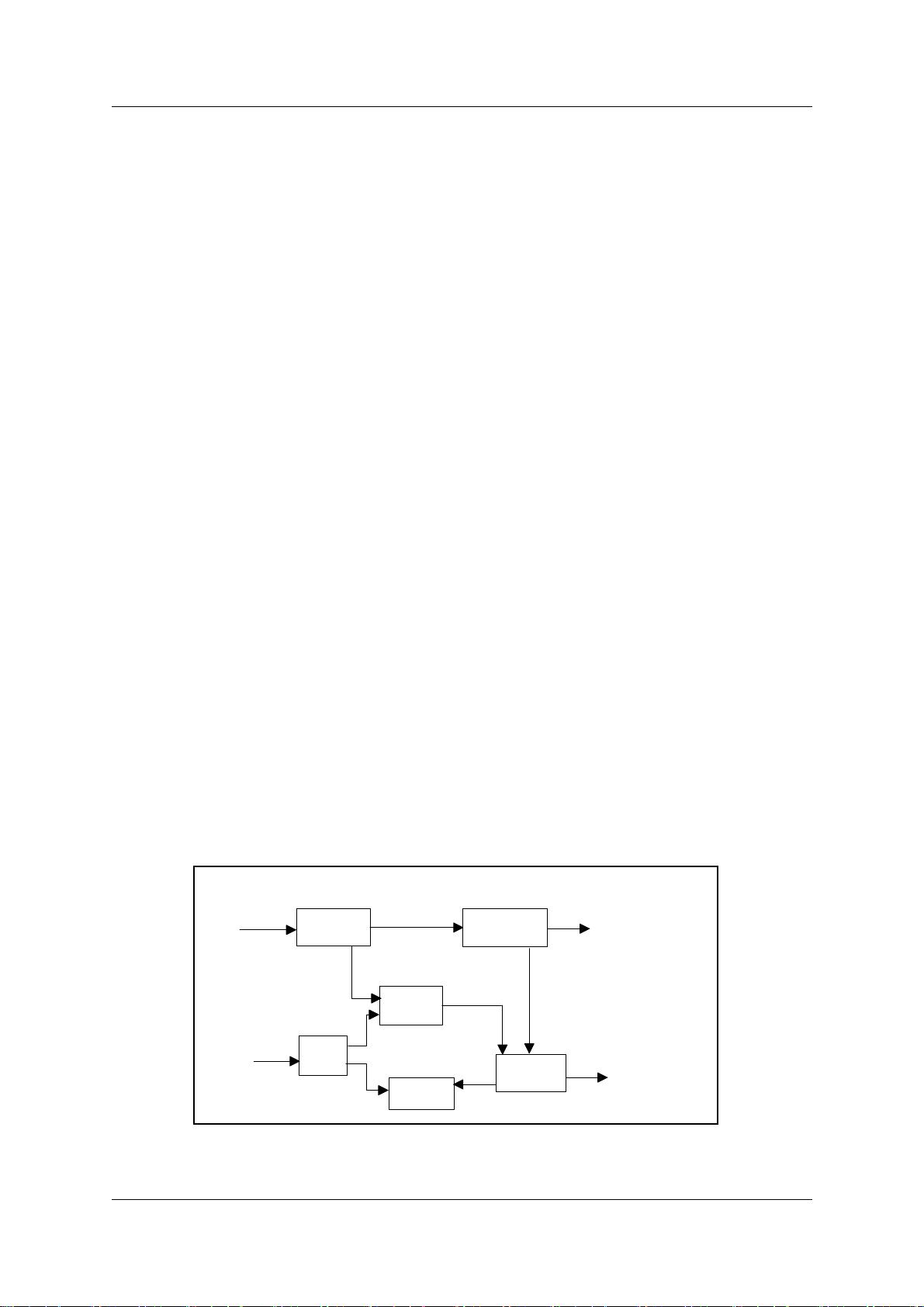

- 第2章至第3章讨论了三种建模方式:结构化、数据流和行为描述。结构化描述适合模块间的交互,数据流描述强调信号的连续流动,而行为描述则关注系统的动态行为。

- 第4章深入解析了运算符,如算术运算符、关系运算符、逻辑运算符、条件运算符和连接运算符,这些都是编程中处理数值和条件判断的基础。

- 第5章至第7章聚焦于模块设计,包括模块的结构、语法、时延以及不同的建模方法(行为、数据流和混合设计)的实例演示。

- 附录A列出了Verilog的保留字,帮助学习者避免在编程时误用这些特殊词汇。

2. 核心知识点:

- 数据类型:包括线网类型和寄存器类型,用于定义变量的不同存储和操作模式。

- 表达式和运算符:理解不同类型的运算符及其优先级对于编写有效代码至关重要。

- 常量和值集合:常量在设计中扮演静态数据的角色,值集合则表示一组可能的数值。

- 格式和注释:良好的代码格式有助于提高可读性和维护性,注释则是解释代码的重要手段。

- 模块设计:模块是构建复杂系统的基本单元,包括输入/输出端口定义和内部结构的描述。

3. 教学目标:

- 通过本教程,读者将掌握如何使用Verilog HDL进行有效的硬件描述,学会如何构建模块、使用运算符和表达式、以及选择合适的建模策略。

4. 适用人群:

- 华为员工或对华为项目有合作的工程师,特别是需要使用Verilog HDL进行数字电路设计的人员。

- 对电子工程感兴趣的学生和初学者,希望了解Verilog HDL作为硬件描述语言的基本原理和实践技巧。

这份教程不仅适用于教学,也是华为内部项目开发过程中不可或缺的参考资料,确保了设计人员能够遵循标准流程并高效地利用Verilog HDL进行硬件设计。

相关推荐

leey20092009

- 粉丝: 0

最新资源

- CCS3.3 CSL库在多版本兼容性应用解析

- 微机室监控机:教学管理设计装置解析

- Pagina-Web-AutoLote:自动化汽车销售平台项目

- Cocos2d-x中Lua脚本的初步使用与变量访问指南

- DZ8前端模板:Bootstrap结构,适配多设备

- inet2源码工具使用教程及训练.ppt

- Python数据分析课程:Timofey Khirianov在MIPT讲授

- Java实现JTA事务控制的示例解析

- LaBSE:实现109种语言的通用句子嵌入技术

- 实现Javascript键值对集合的Map类解析

- LabView实现WebService接口的详细操作指南

- 专业太阳高度角芯片助力太阳能开发

- TensorFlow 2实现自适应梯度剪切技术AGC教程与应用

- 桶型基础独柱结构设计:带压载罐支撑平台解决方案

- LabVIEW数据库访问实例教程完整可用

- Flutter在线商店暗黑风格UI启动套件