Note

Do not write any unlisted values to the JTAG instruction register. Instruction values written to the

MSP430 JTAG register other than those listed above may cause undesired device behavior.

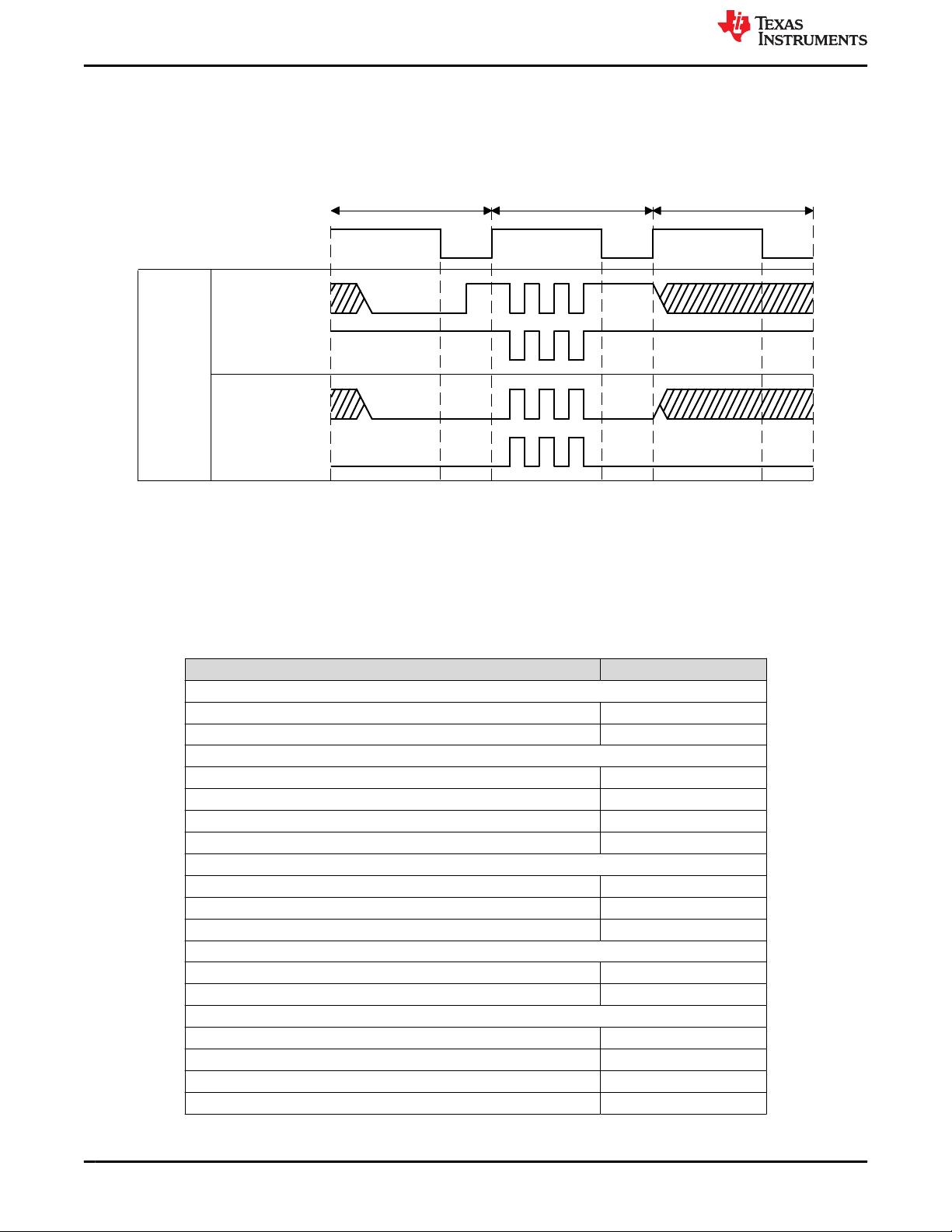

Note

When a new JTAG instruction is shifted into the JTAG instruction register, it takes effect with the

UPDATE-IR state of the TAP controller. When accessing a JTAG data register, the last value written

is captured with the CAPTURE-DR state, and the new value shifted in becomes valid with the

UPDATE-DR state. In other words, there is no need to go through Run-Test/Idle state of the JTAG

TAP controller to shift in instructions or data. Be aware of the fact that clocking TCLK is only possible

in the Run-Test/Idle state. This is why the provided software example application exclusively makes

use of the JTAG macros described in Section 2.2.2, which always go through Run-Test/Idle state.

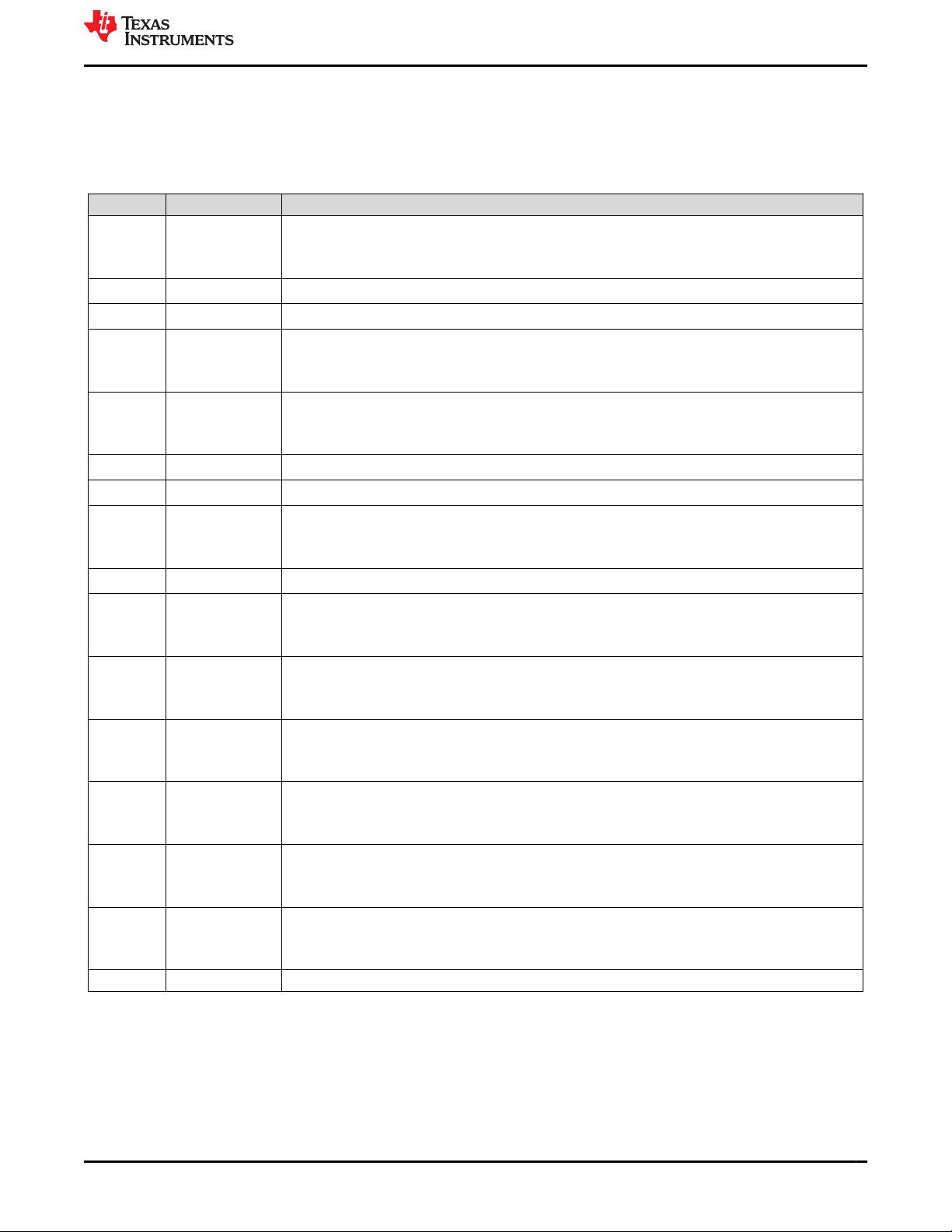

2.2.4.1 Controlling the Memory Address Bus (MAB)

The following instructions control the MAB of the target MSP430. To accomplish this, a 16-bit (or 20-bit in

MSP430X architectures) register, which is called the JTAG MAB register, is addressed. By using the JTAG data

path of the TAP controller, this register can be accessed and modified.

2.2.4.1.1 IR_ADDR_16BIT

This instruction enables setting of the MAB to a specific value, which is shifted in with the next JTAG 16-bit

data access using the DR_SHIFT16 (16-bit Data) macro or the next JTAG 20-bit address word access using the

DR_SHIFT (20-bit Address) macro. The MAB of the MSP430 CPU is set to the value written to the JTAG MAB

register. The previous value stored in the JTAG MAB register is simultaneously shifted out on TDO while the new

16- or 20-bit address is shifted in through TDI.

Note

In MSP430X devices, a 16-bit shift to update the JTAG MAB register does not automatically reset the

upper four bits (19:16) of the JTAG MAB register. Always use the 20-bit shift macro to ensure that the

upper four bits (19:16) are set to a defined value.

2.2.4.1.2 IR_ADDR_CAPTURE

This instruction enables readout of the data on the MAB with the next 16- or 20-bit data access. The MAB value

is not changed during the 16- or 20-bit data access; that is, the 16- or 20-bit data sent on TDI with this command

is ignored (0 is sent as a default in the provided software).

In several places throughout the example code, the IR_ADDR_CAPTURE instruction is also used to set the CPU

to a defined state after accessing the data bus with the IR_DATA_16BIT instruction.

2.2.4.2 Controlling the Memory Data Bus (MDB)

The following instructions control the MDB of the MSP430 CPU. To accomplish this, a 16-bit register, termed

the JTAG MDB register, is addressed. By using the JTAG data path of the TAP controller, this register can be

accessed and modified.

2.2.4.2.1 IR_DATA_TO_ADDR

This instruction enables setting of the MSP430 MDB to a specific value shifted in with the next JTAG 16-bit data

access using the DR_SHIFT16 (16-bit Data) macro. The MDB of the MSP430 CPU is set to the value written to

the JTAG MDB register. As the new value is written into the MDB register, the prior value in the MSP430 MDB

is captured and shifted out on TDO. The MSP430 MAB is set by the value in the JTAG MAB register during

execution of the IR_DATA_TO_ADDR instruction. This instruction is used to write to all memory locations of the

MSP430.

2.2.4.2.2 IR_DATA_16BIT

This instruction enables setting of the MSP430 MDB to the specified 16-bit value shifted in with the next 16-bit

JTAG data access. The complete MSP430 MDB is set to the value of the JTAG MDB register. At the same

www.ti.com

Programming Using the JTAG Interface

SLAU320AJ – JULY 2010 – REVISED MAY 2021

Submit Document Feedback

MSP430™ Programming With the JTAG Interface 15

Copyright © 2021 Texas Instruments Incorporated