Modelsim仿真教程:从入门到10位全加器仿真

需积分: 4 200 浏览量

更新于2024-07-31

收藏 577KB DOC 举报

"Modelsim仿真教程,包括软件使用、Testbench编写、10位全加器功能仿真和课堂作业的完成方法。ModelSim是一款支持VHDL、Verilog、SystemC及混合语言设计文件仿真的工具,通过创建项目、添加对象、编译设计单元和进行仿真来验证硬件设计功能。"

在电子设计自动化(EDA)领域,ModelSim是一款广泛使用的仿真软件,它允许工程师们在硬件描述语言(如VHDL或Verilog)中设计的电路进行功能和时序验证。本教程将详细介绍如何使用ModelSim进行仿真操作。

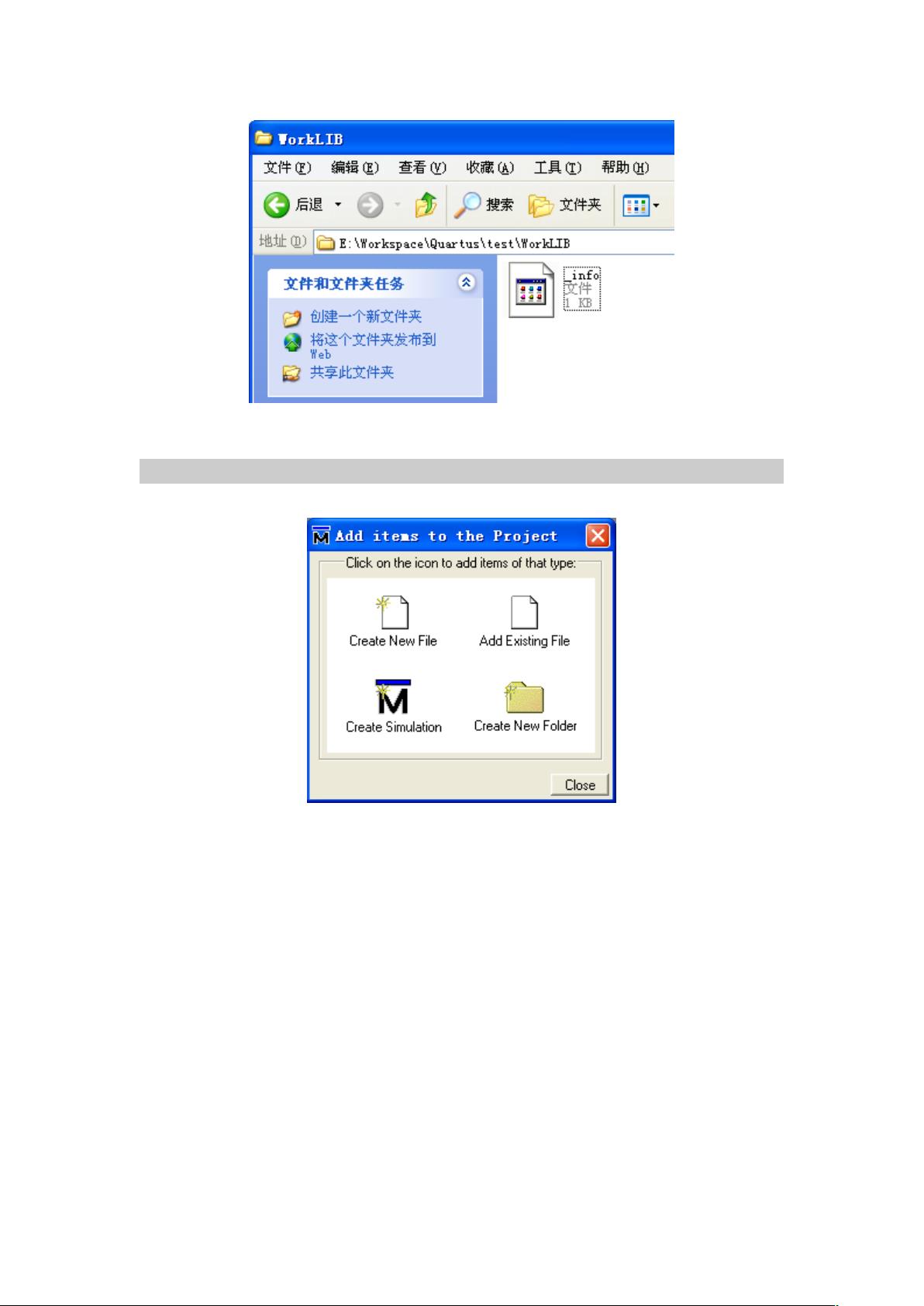

首先,我们需要创建一个新的项目。在ModelSim中,选择“File” > “New” > “Project”。在弹出的对话框中,填入项目名称、位置以及默认库名。工作库是存放编译后设计单元的地方,对于后续的仿真过程至关重要。创建项目后,工作库文件夹会自动建立,其中的"_info"文件标识了该文件夹为ModelSim的工作库。

接下来,我们需要向项目中添加设计文件。可以选择“AddExistingFile”将已有的设计文件导入,或者使用“CreateNewFile”新建设计文件。为了便于文件管理,建议创建新的文件夹("CreateNewFolder")来组织不同类型的文件。

在进行仿真之前,必须先编译设计文件,生成对应的设计单元。编译完成后,这些单元会被添加到工作库中。编译过程包括解析源代码、综合逻辑和生成可执行的仿真模型。

Testbench是验证设计的关键部分,通常用VHDL或Verilog编写,模拟待验证设计的输入和预期输出。Testbench可以设定不同的测试条件,以全面验证设计的正确性。在"Testbench模版"中可以找到编写Testbench的基本结构和技巧。

以10位全加器为例,我们需要创建一个Testbench文件,定义10个输入位和相应的进位输入,然后生成对应的输出,并在ModelSim中运行仿真。仿真过程包括设置仿真时间、启动仿真以及观察波形结果,以确认设计在各种输入条件下的行为是否符合预期。

此外,课堂上布置的作业可能涉及更复杂的设计或特定的仿真需求,根据老师的指导进行相应操作。ModelSim提供了丰富的调试工具,如查看变量值、设置断点和步进执行等,帮助用户深入理解设计的行为。

ModelSim提供了一个强大而直观的环境来验证硬件设计,通过创建项目、编译设计、编写Testbench以及进行仿真,工程师可以确保他们的设计在实际应用前满足功能和性能要求。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2012-11-21 上传

2013-04-26 上传

2022-09-20 上传

2022-07-15 上传

2015-05-28 上传

2013-03-07 上传

hailuo2009

- 粉丝: 0

- 资源: 1

最新资源

- 旅行商问题Python实现

- Didar-309-项目-

- 传送带的PLC程序控制.rar

- riichi:麻雀飜符手役点数计算(日麻和牌点数计算)

- nealbarshes.github.io:GitHub页面

- CORPICECREAM:激励活动指导处处长“萨尔塞多塞科塞多公司的商业生产者”

- Refractor02:重新提交前一张票

- zsh-xah-fly-keys:zsh上的Xah Fly键!

- ant-deb-task:从 code.google.compant-deb-task 自动导出

- 毕业生信息管理系统asp毕业设计(源代码+论文+开题报告+外文翻译+文献综述+答辩PPT).zip

- 工作交接数据库系统.zip

- minikube-client:为Minikube生成客户端证书

- Accuinsight-1.0.3-py2.py3-none-any.whl.zip

- mastermind:请参阅使用D3.js用Javascript编写的Mastermind的新交互式Web版本。

- mycalendar:HTMLに组み込みやすいカレンダー

- 鼠标移动数据光标:在鼠标移动时显示和更新图形标题栏中图像的像素值。-matlab开发